Ad

Boolean variables r010

- 1. Digital Fundamentals Tenth Edition Floyd Chapter 4 © 2008 Pearson Education

- 2. In Boolean algebra, a variable is a symbol used to represent an action, a condition, or data. A single variable can only have a value of 1 or 0. Summary Boolean Addition The complement represents the inverse of a variable and is indicated with an overbar. Thus, the complement of A is A. A literal is a variable or its complement. Addition is equivalent to the OR operation. The sum term is 1 if one or more if the literals are 1. The sum term is zero only if each literal is 0. Determine the values of A, B, and C that make the sum term of the expression A + B + C = 0? Each literal must = 0; therefore A = 1, B = 0 and C = 1.

- 3. In Boolean algebra, multiplication is equivalent to the AND operation. The product of literals forms a product term. The product term will be 1 only if all of the literals are 1. Summary Boolean Multiplication What are the values of the A, B and C if the product term of A.B.C = 1? Each literal must = 1; therefore A = 1, B = 0 and C = 0.

- 4. Summary Commutative Laws In terms of the result, the order in which variables are ORed makes no difference. The commutative laws are applied to addition and multiplication. For addition, the commutative law states A + B = B + A In terms of the result, the order in which variables are ANDed makes no difference. For multiplication, the commutative law states AB = BA

- 5. Summary Associative Laws When ORing more than two variables, the result is the same regardless of the grouping of the variables. The associative laws are also applied to addition and multiplication. For addition, the associative law states A + (B +C) = (A + B) + C For multiplication, the associative law states When ANDing more than two variables, the result is the same regardless of the grouping of the variables. A(BC) = (AB)C

- 6. Summary Distributive Law The distributive law is the factoring law. A common variable can be factored from an expression just as in ordinary algebra. That is AB + AC = A(B+ C) The distributive law can be illustrated with equivalent circuits: B+ C C A X B AB B X A C A AC AB + AC A(B+ C)

- 7. Summary Rules of Boolean Algebra 1. A + 0 = A 2. A + 1 = 1 3. A . 0 = 0 4. A . 1 = 1 5. A + A = A 7. A . A = A 6. A + A = 1 8. A . A = 0 9. A = A = 10. A + AB = A 12. (A + B)(A + C) = A + BC 11. A + AB = A + B

- 8. Summary Rules of Boolean Algebra Rules of Boolean algebra can be illustrated with Venn diagrams. The variable A is shown as an area. The rule A + AB = A can be illustrated easily with a diagram. Add an overlapping area to represent the variable B. A B AB The overlap region between A and B represents AB. A A B A B AB The diagram visually shows that A + AB = A. Other rules can be illustrated with the diagrams as well. =

- 9. A Summary Rules of Boolean Algebra A + AB = A + B This time, A is represented by the blue area and B again by the red circle. B The intersection represents AB. Notice that A + AB = A + B A AB A Illustrate the rule with a Venn diagram.

- 10. Summary Rules of Boolean Algebra Rule 12, which states that (A + B)(A + C) = A + BC, can be proven by applying earlier rules as follows: (A + B)(A + C) = AA + AC + AB + BC = A + AC + AB + BC = A(1 + C + B) + BC = A . 1 + BC = A + BC This rule is a little more complicated, but it can also be shown with a Venn diagram, as given on the following slide…

- 11. Summary A B C A A + B The area representing A + B is shown in yellow. The area representing A + C is shown in red. Three areas represent the variables A, B, and C. A C A + C The overlap of red and yellow is shown in orange. A B C A B C BC ORing with A gives the same area as before. A B C BC = A B C (A + B)(A + C) A + BC The overlapping area between B and C represents BC.

- 12. Summary DeMorgan’s Theorem The complement of a product of variables is equal to the sum of the complemented variables. DeMorgan’s 1st Theorem AB = A + B Applying DeMorgan’s first theorem to gates: Output Inputs A B AB A + B 0 0 1 1 0 1 0 1 1 1 1 0 1 1 1 0 A + B A B AB A B NAND Negative-OR

- 13. Summary DeMorgan’s Theorem DeMorgan’s 2nd Theorem The complement of a sum of variables is equal to the product of the complemented variables. A + B = A . B Applying DeMorgan’s second theorem to gates: A B A + B AB Output Inputs 0 0 1 1 0 1 0 1 1 0 0 0 1 0 0 0 AB A B A + B A B NOR Negative-AND

- 14. Summary Apply DeMorgan’s theorem to remove the overbar covering both terms from the expression X = C + D. DeMorgan’s Theorem To apply DeMorgan’s theorem to the expression, you can break the overbar covering both terms and change the sign between the terms. This results in X = C . D. Deleting the double bar gives X = C . D. =

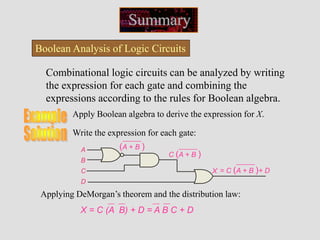

- 15. A C D B Summary Boolean Analysis of Logic Circuits Combinational logic circuits can be analyzed by writing the expression for each gate and combining the expressions according to the rules for Boolean algebra. Apply Boolean algebra to derive the expression for X. Write the expression for each gate: Applying DeMorgan’s theorem and the distribution law: C (A + B ) = C (A + B )+ D (A + B ) X = C (A B) + D = A B C + D X

- 16. Summary Boolean Analysis of Logic Circuits Use Multisim to generate the truth table for the circuit in the previous example. Set up the circuit using the Logic Converter as shown. (Note that the logic converter has no “real-world” counterpart.) Double-click the Logic Converter top open it. Then click on the conversion bar on the right side to see the truth table for the circuit (see next slide).

- 17. Summary Boolean Analysis of Logic Circuits The simplified logic expression can be viewed by clicking Simplified expression

- 18. Summary SOP and POS forms Boolean expressions can be written in the sum-of-products form (SOP) or in the product-of-sums form (POS). These forms can simplify the implementation of combinational logic, particularly with PLDs. In both forms, an overbar cannot extend over more than one variable. An expression is in SOP form when two or more product terms are summed as in the following examples: An expression is in POS form when two or more sum terms are multiplied as in the following examples: A B C + A B A B C + C D C D + E (A + B)(A + C) (A + B + C)(B + D) (A + B)C

- 19. Summary SOP Standard form In SOP standard form, every variable in the domain must appear in each term. This form is useful for constructing truth tables or for implementing logic in PLDs. You can expand a nonstandard term to standard form by multiplying the term by a term consisting of the sum of the missing variable and its complement. Convert X = A B + A B C to standard form. The first term does not include the variable C. Therefore, multiply it by the (C + C), which = 1: X = A B (C + C) + A B C = A B C + A B C + A B C

- 20. Summary SOP Standard form The Logic Converter in Multisim can convert a circuit into standard SOP form. Click the truth table to logic button on the Logic Converter. Use Multisim to view the logic for the circuit in standard SOP form. See next slide…

- 22. Summary POS Standard form In POS standard form, every variable in the domain must appear in each sum term of the expression. You can expand a nonstandard POS expression to standard form by adding the product of the missing variable and its complement and applying rule 12, which states that (A + B)(A + C) = A + BC. Convert X = (A + B)(A + B + C) to standard form. The first sum term does not include the variable C. Therefore, add C C and expand the result by rule 12. X = (A + B + C C)(A + B + C) = (A +B + C )(A + B + C)(A + B + C)

- 23. The Karnaugh map (K-map) is a tool for simplifying combinational logic with 3 or 4 variables. For 3 variables, 8 cells are required (23). The map shown is for three variables labeled A, B, and C. Each cell represents one possible product term. Each cell differs from an adjacent cell by only one variable. ABC ABC ABC ABC ABC ABC ABC ABC Summary Karnaugh maps

- 24. 0 1 00 01 11 10 AB C Cells are usually labeled using 0’s and 1’s to represent the variable and its complement. Gray code Summary Karnaugh maps Ones are read as the true variable and zeros are read as the complemented variable. The numbers are entered in gray code, to force adjacent cells to be different by only one variable.

- 25. Summary ABC ABC ABC ABC ABC ABC ABC ABC AB AB AB AB C C Alternatively, cells can be labeled with the variable letters. This makes it simple to read, but it takes more time preparing the map. Karnaugh maps C C AB AB AB AB C C AB AB AB AB ABC ABC Read the terms for the yellow cells. The cells are ABC and ABC.

- 26. 1. Group the 1’s into two overlapping groups as indicated. 2. Read each group by eliminating any variable that changes across a boundary. 3. The vertical group is read AC. Summary K-maps can simplify combinational logic by grouping cells and eliminating variables that change. Karnaugh maps 1 1 1 AB C 00 01 11 10 0 1 1 1 1 AB C 00 01 11 10 0 1 Group the 1’s on the map and read the minimum logic. B changes across this boundary C changes across this boundary 4. The horizontal group is read AB. X = AC +AB

- 27. A 4-variable map has an adjacent cell on each of its four boundaries as shown. AB AB AB AB CD CD CD CD Each cell is different only by one variable from an adjacent cell. Grouping follows the rules given in the text. The following slide shows an example of reading a four variable map using binary numbers for the variables… Summary Karnaugh maps

- 28. X Summary Karnaugh maps Group the 1’s on the map and read the minimum logic. 1. Group the 1’s into two separate groups as indicated. 2. Read each group by eliminating any variable that changes across a boundary. 3. The upper (yellow) group is read as AD. 4. The lower (green) group is read as AD. AB CD 00 01 11 10 00 01 11 10 1 1 1 1 1 1 1 1 AB CD 00 01 11 10 00 01 11 10 1 1 1 1 1 1 1 1 X = AD +AD B changes C changes B changes C changes across outer boundary

- 29. Summary Hardware Description Languages (HDLs) A Hardware Description Language (HDL) is a tool for implementing a logic design in a PLD. One important language is called VHDL. In VHDL, there are three approaches to describing logic: 2. Dataflow 3. Behavioral 1. Structural Description is like a schematic (components and block diagrams). Description is equations, such as Boolean operations, and registers. Description is specifications over time (state machines, etc.).

- 30. Summary Hardware Description Languages (HDLs) The data flow method for VHDL uses Boolean-type statements. There are two-parts to a basic data flow program: the entity and the architecture. The entity portion describes the I/O. The architecture portion describes the logic. The following example is a VHDL program showing the two parts. The program is used to detect an invalid BCD code. entity BCDInv is port (B,C,D: in bit; X: out bit); end entity BCDInv architecture Invalid of BCDInv begin X <= (B or C) and D; end architecture Invalid;

- 31. Summary Hardware Description Languages (HDLs) Another standard HDL is Verilog. In Verilog, the I/O and the logic is described in one unit called a module. Verilog uses specific symbols to stand for the Boolean logical operators. The following is the same program as in the previous slide, written for Verilog: module BCDInv (X, B, C, D); input B, C, D; output X; assign X = (B | C)&D; endmodule

- 32. Selected Key Terms Variable Complement Sum term Product term A symbol used to represent a logical quantity that can have a value of 1 or 0, usually designated by an italic letter. The inverse or opposite of a number. In Boolean algebra, the inverse function, expressed with a bar over the variable. The Boolean sum of two or more literals equivalent to an OR operation. The Boolean product of two or more literals equivalent to an AND operation.

- 33. Selected Key Terms Sum-of- products (SOP) Product of sums (POS) Karnaugh map VHDL A form of Boolean expression that is basically the ORing of ANDed terms. A form of Boolean expression that is basically the ANDing of ORed terms. An arrangement of cells representing combinations of literals in a Boolean expression and used for systematic simplification of the expression. A standard hardware description language. IEEE Std. 1076-1993.

- 34. 1. The associative law for addition is normally written as a. A + B = B + A b. (A + B) + C = A + (B + C) c. AB = BA d. A + AB = A © 2008 Pearson Education

- 35. 2. The Boolean equation AB + AC = A(B+ C) illustrates a. the distribution law b. the commutative law c. the associative law d. DeMorgan’s theorem © 2008 Pearson Education

- 36. 3. The Boolean expression A . 1 is equal to a. A b. B c. 0 d. 1 © 2008 Pearson Education

- 37. 4. The Boolean expression A + 1 is equal to a. A b. B c. 0 d. 1 © 2008 Pearson Education

- 38. 5. The Boolean equation AB + AC = A(B+ C) illustrates a. the distribution law b. the commutative law c. the associative law d. DeMorgan’s theorem © 2008 Pearson Education

- 39. 6. A Boolean expression that is in standard SOP form is a. the minimum logic expression b. contains only one product term c. has every variable in the domain in every term d. none of the above © 2008 Pearson Education

- 40. © 2008 Pearson Education 7. Adjacent cells on a Karnaugh map differ from each other by a. one variable b. two variables c. three variables d. answer depends on the size of the map

- 41. © 2008 Pearson Education C C AB AB AB AB 1 1 1 1 8. The minimum expression that can be read from the Karnaugh map shown is a. X = A b. X = A c. X = B d. X = B

- 42. © 2008 Pearson Education 9. The minimum expression that can be read from the Karnaugh map shown is a. X = A b. X = A c. X = B d. X = B C C AB AB AB AB 1 1 1 1

- 43. © 2008 Pearson Education 10. In VHDL code, the two main parts are called the a. I/O and the module b. entity and the architecture c. port and the module d. port and the architecture

- 44. Answers: 1. b 2. c 3. a 4. d 5. a 6. c 7. a 8. a 9. d 10. b