A meta model supporting both hardware and smalltalk-based execution of FPGA circuits

- 1. A META MODEL SUPPORTING BOTH HARDWARE AND SMALLTALK-BASED EXECUTION OF FPGA CIRCUITS Le Xuan Sang1,2 Loïc Lagadec1 , Luc Fabress2 , Jannik Laval2 and Noury Bouraqadi2 1 Lab-STICC, ENSTA Bretagne 2 Institut Mines-Telecom, Mines Douai

- 2. ABOUT ME • LE Xuan Sang • 2014-2017 PHD student • Coupling FPGA / Smalltalk in robotic applications FPGA Application Processor Abstraction Synthesis Application 2

- 3. -- libraries declararion library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL ; -- Entity declaration entity SimpleALU is port ( clk:in std_logic; A,B:in std_logic_vector(31 downto 0); opcode:in std_logic; R:out std_logic_vector(31 downto 0) ); end SimpleALU; -- Architecture architecture arch of SimpleALU is Signal r1,r2,r3:signed(31 downto 0) :=(others=>'0'); begin r1<=signed(A); r2<=signed(B); R<=std_logic_vector(r3); process(clk) begin if rising_edge(clk) then case opcode is when '0' => r3<=(r1+r2); when '1' => r3<= r1 AND r2; when others => (others=>'0'); end case; end if; end process; end architecture; DESCRIPTION OF A CIRCUIT USING VHDL ALU A B R opcode clk Interface 3

- 4. Components -- libraries declararion library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL ; -- Entity declaration entity SimpleALU is port ( clk:in std_logic; A,B:in std_logic_vector(31 downto 0); opcode:in std_logic; R:out std_logic_vector(31 downto 0) ); end SimpleALU; -- Architecture architecture arch of SimpleALU is Signal r1,r2,r3:signed(31 downto 0) :=(others=>'0'); begin r1<=signed(A); r2<=signed(B); R<=std_logic_vector(r3); process(clk) begin if rising_edge(clk) then case opcode is when '0' => r3<=(r1+r2); when '1' => r3<= r1 AND r2; when others => (others=>'0'); end case; end if; end process; end architecture; DESCRIPTION OF A CIRCUIT USING VHDL • Operated in parallel • Activated when its inputs change • Signals assignment alway need a propagation delay to take effect ALU A B R opcode clk Interface 3

- 5. FPGA CIRCUIT MODELLING 3 problems (1) The meta-model must capture both the structure and the behaviour of the circuit (2) The parallel characteristics + propagation delay of the FPGA circuits must be taken into account (3) Transparent execution of the circuit on FPGA 4 1 alu := SimpleALU new. 2 alu A:20. 3 alu B:15. 4 alu opcode:false. "add" 5 alu execute. 6 alu R asInteger "35" ALU A B R opcode clk Execute on FPGA FPGA available ? Outputs No Yes 3 2 1 Simulated execution on VM

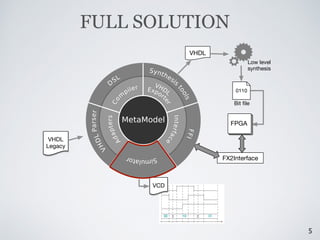

- 6. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 7. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 8. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 9. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 10. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 11. FULL SOLUTION VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 5

- 12. SMALLTALK-BASED EXECUTION OF THE FPGA CIRCUIT MODEL

- 13. EVENT-DRIVEN FOR PROPAGATION EXECUTION • All parallel components are considered as processes with sensitivity list (event listener) • The value of signals is changed only after update • Events occur on signals change • All processes that have changed signals as inputs will become active • Execution of a triggered process may trigger other processes Update signals value Determine events occur Execute processes triggered by events Start End 6

- 14. CIRCUIT MODEL EXECUTION • Inputs ports are assigned at the first time • Each circuit has a done signal • The circuit is triggered by the clock clk • The execution is repeated until the done signal is asserted alu := SimpleALU new. alu A:20. alu B:15. alu opcode:false. alu execute. 7

- 15. HARDWARE-BASED EXECUTION OF THE FPGA CIRCUIT MODEL

- 16. AUTOMATIC DEPLOYEMENT ON FPGA 1. Generate automatically the communication interface 2. TheVHDL codes is exported from the model 3. The hardware configuration is generated 4. The vendor tool-chain is used for low level synthesis SimpleALU Interface RA B opcode Final circuit Low level synthesis 0110 Bit file FPGA VHDL HW. configuration Export Program 8 No effort for developper

- 17. HARDWARE BASED EXECUTION OF CIRCUIT MODEL 1. The inputs signals are assigned 2. The input values are encode as ByteArray and sent to FPGA 3. The interface circuit decodes the data it received and sends to the target circuit 4. The outputs of the circuit can be fetched from Smalltalk in a reverse way #[<A>,<B>,<opcode>] #[<R>] SimpleALU RA B opcode Interface Pharo VM 9

- 19. POST-MORTEM ANALYSIS OF SIMULATION • The circuit is executed for a specific amount of time • The inputs are changed at some specific points of time • Next input changes are stored in a time queue • Timing information and signals values are traced continuously into aVCD file alu := SimpleALU new. queue := { #clk clock: 50ns. #A change:{1. 3. 5. 7} every:50ns. #B change:{0. 2. 4. 6} every:50ns. #opcode change:{'0'.'1'} every:100ns. } asTimeQueueFor:400ns. stream := WaveFormStream on:'ALU.vcd'. alu modellingExecution:#execute timeQueue:queue dumpOn:stream. 10

- 20. HARDWARE BREAKPOINT • How can we manually stop the execution of FPGA circuit ? • Enables the software like debug capabilities on hardware 11

- 21. HARDWARE BREAKPOINT • How can we manually stop the execution of FPGA circuit ? • Enables the software like debug capabilities on hardware 11 Target circuit Clock controller global clock clk

- 22. HARDWARE BREAKPOINT • How can we manually stop the execution of FPGA circuit ? • Enables the software like debug capabilities on hardware 11 Target circuit Clock controller global clock clk

- 23. STATIC BREAKPOINT …… SimpleCounter>>execute <hdl:#combinational> {self clk. self reset. self start} onChange: [ self reset = '1' ifTrue:[ cnt reset:'0'. ] ifFalse:[ self start = '1' ifTrue:[ cnt reset:'0'. done <- false. ] ifFalse:[ cnt = 100 ifTrue:[ done <- true. ] ifFalse:[ cnt <- (cnt +1).] cnt = 4 ifTrue:[ self halt. ] ] ] ] dout <- cnt. Halting A simple counter 12

- 24. STATIC BREAKPOINT …… SimpleCounter>>execute <hdl:#combinational> {self clk. self reset. self start} onChange: [ self reset = '1' ifTrue:[ cnt reset:'0'. ] ifFalse:[ self start = '1' ifTrue:[ cnt reset:'0'. done <- false. ] ifFalse:[ cnt = 100 ifTrue:[ done <- true. ] ifFalse:[ cnt <- (cnt +1).] cnt = 4 ifTrue:[ self halt. ] ] ] ] dout <- cnt. Halting • Need to re-synthesize the circuit when changing Interface Target circuit Clock controller halt global clock clk clock counter done start Inputs Output 12 A simple counter

- 25. DYNAMIC BREAKPOINT obj := SimpleCounter new. obj setBreakpointOn:#dout value:4. obj enableBreakpointOn:#dout. obj execute. "stop at breakpoint” “set another breakpoint” obj setBreakpointOn:#dout value:10. obj resume. "resume the execution” “stop when out = 10” obj resume. "Continue” 13

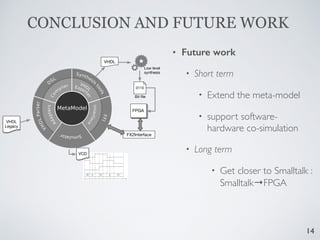

- 26. • Future work • Short term • Extend the meta-model • support software- hardware co-simulation • Long term • Get closer to Smalltalk : Smalltalk→FPGA CONCLUSION AND FUTURE WORK VHDL Legacy VCD VHDL 0110 Bit file Low level synthesis FPGA FX2Interface MetaModel Interface Adapters Export er VHDL Co m piler Synthesis tools D SL VHDLParser Simulator FFI 14

- 27. A META MODEL SUPPORTING BOTH HARDWARE AND SMALLTALK-BASED EXECUTION OF FPGA CIRCUITS Le Xuan Sang1,2 Loïc Lagadec1 , Luc Fabress2 , Jannik Laval2 and Noury Bouraqadi2 1 Lab-STICC, ENSTA Bretagne 2 Institut Mines-Telecom, Mines Douai

- 28. 1. Source code analysis. 2. Resource allocation. 3. Scheduling. 4. Resource binding 5. Generate appropriate interface between application and the circuit 6. Modelling and simulation FPGA circuit at RTL level. HIGH LEVEL SYNTHESIS FRAMEWORK Workingprogress

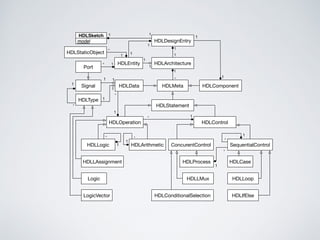

- 29. • Based on the IEEE 1076.66 RTL synthesis standard (VHDL-87) • Support almost anyVHDL structures in the standard • Each meta-description in the meta-model capture both structure and behaviour of a circuit element • Signals and Ports are modelled by objects with history META-MODEL (1)

- 30. Dedicated DSL for circuit description META-MODEL (2) HDLSketch subclass: #SimpleALU instanceVariableNames: 'r1 r2 r3' SimpleALU>>setUpPorts self in:{#A.#B}of:(LogicVector size:32). self in:#opcode of:Logic new. self out:#R of:(LogicVector size:32) SimpleALU>>setUpSignals r1 := Signal of:(LogicVector size:32 signed:true). r2 := Signal of:(LogicVector size:32 signed:true). r3 := Signal of:(LogicVector size:32 signed:true). SimpleALU>>execute <hdl:#combinational> r1 <- (self A). r2 <- (self B). self R <- r3. {self clk} onChange:[ self done <- false. self clk posedge ifTrue:[ self opcode caseOf: { ['0'] -> [r3 <- (r1 + r2)]. ['1'] -> [r3 <- (r1 and:r2)]. }. self done <- true. ]]. DSL 1 HDLSketch class » compile:text 2 classified:aCategory 3 notifying:requestor 4 |ast| 5 ast := self compiler parse: text. 6 (ast hasPragmaNamed: #hdl:) ifTrue:[ 7 ModelBuilder for:self 8 ast:ast notificator:requestor. 9 ˆself compiledMethodFor:ast selector. 10 ]. 11 ˆsuper compile:text 12 classified:aCategory 13 notifying:requestor. Error report Syntax analysis Model generation Circuit checking Executable code generation error Ok Ok error

- 31. • Reuse of Legacy VHDL • A builtinVHDL Parser (based on PetitParser). • Third-partyVHDL codes with respect to the IEEE 1076.66 RTL standard can be converted to our circuit-model. • Updated: the converted circuit model now can be simulated in our environment META-MODEL (3)

- 32. EXAMPLE HDLSketch subclass: #SimpleCounter instanceVariableNames: 'cnt' SimpleCounter>>setupPorts self out:#dout of:(LogicVector size:32). SimpleCounter>>setupSignals cnt := Signal of:(LogicVector size:32). SimpleCounter>>execute <hdl:#combinational> {self clk. self reset. self start} onChange: [ self reset = '1' ifTrue:[ cnt reset:'0'. ] ifFalse:[ self start = '1' ifTrue:[ cnt reset:'0'. done <- false. ] ifFalse:[ cnt = 100 ifTrue:[ done <- true. ] ifFalse:[ cnt <- (cnt +1).] ] ] ] dout <- cnt. A counter from 0 to 100

- 33. DYNAMIC BREAKPOINT obj := SimpleCounter new. obj setBreakpointOn:#dout value:4. obj enableBreakpointOn:#dout. obj execute. "stop at breakpoint" obj resume. "resume the execution" MUX Target circuit = = = output 1 output 2 output m … … ref. 1 ref. 2 ref. m select Clock controller break global clock resume clk Debug sub-circuit start done clock counter Breakpoint controllerInterface Inputs Outputs 13

- 34. DYNAMIC BREAKPOINT obj := SimpleCounter new. obj setBreakpointOn:#dout value:4. obj enableBreakpointOn:#dout. obj execute. "stop at breakpoint" obj resume. "resume the execution" MUX Target circuit = = = output 1 output 2 output m … … ref. 1 ref. 2 ref. m select Clock controller break global clock resume clk Debug sub-circuit start done clock counter Breakpoint controllerInterface Inputs Outputs 13

![HARDWARE BASED EXECUTION OF

CIRCUIT MODEL

1. The inputs signals are assigned

2. The input values are encode as

ByteArray and sent to FPGA

3. The interface circuit decodes the

data it received and sends to the

target circuit

4. The outputs of the circuit can be

fetched from Smalltalk in a

reverse way

#[<A>,<B>,<opcode>] #[<R>]

SimpleALU

RA B opcode

Interface

Pharo VM

9](https://image.slidesharecdn.com/2-151027170425-lva1-app6891/85/A-meta-model-supporting-both-hardware-and-smalltalk-based-execution-of-FPGA-circuits-17-320.jpg)

![STATIC BREAKPOINT

……

SimpleCounter>>execute

<hdl:#combinational>

{self clk. self reset. self start} onChange:

[

self reset = '1' ifTrue:[

cnt reset:'0'.

] ifFalse:[

self start = '1' ifTrue:[

cnt reset:'0'.

done <- false.

] ifFalse:[

cnt = 100 ifTrue:[

done <- true.

] ifFalse:[

cnt <- (cnt +1).]

cnt = 4 ifTrue:[

self halt.

]

]

]

]

dout <- cnt.

Halting

A simple counter

12](https://image.slidesharecdn.com/2-151027170425-lva1-app6891/85/A-meta-model-supporting-both-hardware-and-smalltalk-based-execution-of-FPGA-circuits-23-320.jpg)

![STATIC BREAKPOINT

……

SimpleCounter>>execute

<hdl:#combinational>

{self clk. self reset. self start} onChange:

[

self reset = '1' ifTrue:[

cnt reset:'0'.

] ifFalse:[

self start = '1' ifTrue:[

cnt reset:'0'.

done <- false.

] ifFalse:[

cnt = 100 ifTrue:[

done <- true.

] ifFalse:[

cnt <- (cnt +1).]

cnt = 4 ifTrue:[

self halt.

]

]

]

]

dout <- cnt.

Halting

• Need to re-synthesize the circuit

when changing

Interface

Target

circuit

Clock

controller

halt

global clock

clk

clock

counter

done

start

Inputs Output

12

A simple counter](https://image.slidesharecdn.com/2-151027170425-lva1-app6891/85/A-meta-model-supporting-both-hardware-and-smalltalk-based-execution-of-FPGA-circuits-24-320.jpg)

![Dedicated DSL for circuit description

META-MODEL (2)

HDLSketch subclass: #SimpleALU

instanceVariableNames: 'r1 r2 r3'

SimpleALU>>setUpPorts

self in:{#A.#B}of:(LogicVector size:32).

self in:#opcode of:Logic new.

self out:#R of:(LogicVector size:32)

SimpleALU>>setUpSignals

r1 := Signal of:(LogicVector size:32 signed:true).

r2 := Signal of:(LogicVector size:32 signed:true).

r3 := Signal of:(LogicVector size:32 signed:true).

SimpleALU>>execute

<hdl:#combinational>

r1 <- (self A).

r2 <- (self B).

self R <- r3.

{self clk} onChange:[

self done <- false.

self clk posedge ifTrue:[

self opcode caseOf: {

['0'] -> [r3 <- (r1 + r2)].

['1'] -> [r3 <- (r1 and:r2)].

}.

self done <- true.

]].

DSL

1 HDLSketch class » compile:text

2 classified:aCategory

3 notifying:requestor

4 |ast|

5 ast := self compiler parse: text.

6 (ast hasPragmaNamed: #hdl:) ifTrue:[

7 ModelBuilder for:self

8 ast:ast notificator:requestor.

9 ˆself compiledMethodFor:ast selector.

10 ].

11 ˆsuper compile:text

12 classified:aCategory

13 notifying:requestor.

Error

report

Syntax analysis

Model generation

Circuit checking

Executable code generation

error

Ok

Ok

error](https://image.slidesharecdn.com/2-151027170425-lva1-app6891/85/A-meta-model-supporting-both-hardware-and-smalltalk-based-execution-of-FPGA-circuits-30-320.jpg)

![EXAMPLE

HDLSketch subclass: #SimpleCounter

instanceVariableNames: 'cnt'

SimpleCounter>>setupPorts

self out:#dout of:(LogicVector size:32).

SimpleCounter>>setupSignals

cnt := Signal of:(LogicVector size:32).

SimpleCounter>>execute

<hdl:#combinational>

{self clk. self reset. self start} onChange:

[

self reset = '1' ifTrue:[

cnt reset:'0'.

] ifFalse:[

self start = '1' ifTrue:[

cnt reset:'0'.

done <- false.

] ifFalse:[

cnt = 100 ifTrue:[

done <- true.

] ifFalse:[

cnt <- (cnt +1).]

]

]

]

dout <- cnt.

A counter from 0 to 100](https://image.slidesharecdn.com/2-151027170425-lva1-app6891/85/A-meta-model-supporting-both-hardware-and-smalltalk-based-execution-of-FPGA-circuits-32-320.jpg)