APB protocol v1.0

Download as ODP, PDF12 likes26,293 views

The document describes conventions and signals used in the AMBA 3 APB protocol specification version 1.0. It summarizes write and read transfer procedures, including optional wait states using the PREADY signal. Error responses are also described. The operating states of the APB include IDLE, SETUP, and ACCESS states. PREADY controls exiting the ACCESS state.

1 of 29

Downloaded 783 times

![Mapping of PSLVERR

● When bridging:

● From AXI to APB An APB error is mapped back to

RRESP/BRESP = SLVERR. This is achieved by mapping

PSLVERR to the AXI signals RRESP[1] for reads and

BRESP[1] for writes.

● From AHB to APB PSLVERR is mapped back to HRESP =

ERROR for both reads and writes. This is ac](https://image.slidesharecdn.com/apbppt-151203045605-lva1-app6892/85/APB-protocol-v1-0-24-320.jpg)

Ad

Recommended

Advance Peripheral Bus

Advance Peripheral Bus SIVA NAGENDRA REDDY The Advanced Microcontroller Bus Architecture (AMBA) specification defines interfaces for connecting processor and peripherals. It aims to standardize connections to enable modular system design. The Advanced Peripheral Bus (APB) is defined by AMBA for simple peripherals like timers and I/O. It uses few signals for non-pipelined transfers in two cycles to reduce power and complexity.

AMBA 3 APB Protocol

AMBA 3 APB ProtocolSwetha GSM The Advanced Peripheral Bus (APB) is part of the Advanced Microcontroller Bus Architecture (AMBA) protocol family. It defines a low-cost interface that is optimized for minimal power consumption and reduced interface complexity.

System verilog coverage

System verilog coveragePushpa Yakkala Coverage is a technique used in simulation to measure how much of a design has been tested or verified. There are different types of coverage including functional coverage, which checks which features or functions have been tested, and code coverage, which measures how much of the design code has been exercised. Coverage is measured using coverage tools and reports to identify any remaining gaps or "holes" that need additional testing to fully verify the design.

Introduction about APB Protocol

Introduction about APB ProtocolPushpa Yakkala The Advanced Peripheral Bus (APB) is a low-cost, low-power interface defined by ARM for connecting peripherals to processors. It provides an unpipelined bus with signals that only transition on the rising edge of the clock. Peripherals on the APB can extend transfers using the PREADY signal. The APB supports both read and write transfers, and peripherals can indicate transfer errors using the PSLVERR signal.

Session 6 sv_randomization

Session 6 sv_randomizationNirav Desai This document discusses randomization using SystemVerilog. It begins by introducing constraint-driven test generation and random testing. It explains that SystemVerilog allows specifying constraints in a compact way to generate random values that meet the constraints. The document then discusses using objects to model complex data types for randomization. It provides examples of using SystemVerilog functions like $random, $urandom, and $urandom_range to generate random numbers. It also discusses constraining randomization using inline constraints and randomizing objects with the randomize method.

Apb

ApbAzad Mishra The document describes the AMBA 3 APB protocol. It has an unpipelined design to reduce complexity and power consumption. Transfers take at least two cycles with the first being a setup phase and second an access phase controlled by the PENABLE signal. Slaves can extend transfers using the PREADY signal. Errors are indicated by PSLVERR. The protocol defines read and write transfers with or without wait states.

Serial Peripheral Interface(SPI)

Serial Peripheral Interface(SPI)Dhaval Kaneria The SPI (Serial Peripheral Interface) is a synchronous serial communication protocol used for communication between devices. It uses a master-slave architecture with a single master device initiating data transfer. Key features include using separate clock and data lines, operating in full duplex mode, and allowing multiple slave devices through individual chip selects. It provides a lower pin count solution than parallel buses at the cost of slower communication speeds.

Session 7 code_functional_coverage

Session 7 code_functional_coverageNirav Desai This document discusses code coverage and functional coverage. It defines code coverage as measuring how much of the source code is tested by verification. It describes different types of code coverage like statement coverage, block coverage, conditional coverage, branch coverage, path coverage, toggle coverage and FSM coverage. It then discusses functional coverage, which measures how much of the specification is covered, rather than just the code. It notes some advantages of functional coverage over code coverage.

AMBA 2.0 PPT

AMBA 2.0 PPTNirav Desai This document describes the implementation of an Advanced High Performance Bus (AHB) protocol using Verilog. It discusses the key components and signals of the AHB, including masters, slaves, arbiters, decoders, request/grant protocols, and pipelined transactions. It also provides RTL diagrams and simulation results for the arbiter, decoder, and multiplexer modules. The goal is to develop a synthesizable Verilog model of the AHB to allow easy addition of new blocks and improve bus efficiency through pipelined transactions.

Ambha axi

Ambha axiHARINATH REDDY Advanced eXtensible Interface (AXI), part of the ARM Advanced Microcontroller Bus Architecture (AMBA3) (AXI3) and 4 (AXI4) specifications.

AXI Protocol.pptx

AXI Protocol.pptxYazan Yousef A presentation about the AXI protocol includes all the signal description and explanation referred to the AXI specification

AMBA Ahb 2.0

AMBA Ahb 2.0Akhil Srivastava This document describes the Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB) 2.0 specification. It details features of AHB such as burst transfers, split transactions, and single-cycle bus master handover. It also explains typical components in an AMBA AHB system including masters, slaves, arbitration, and bus operation with different transfer types.

AMBA_APB_pst

AMBA_APB_pstBynaboina Krishna This document discusses the Advanced Peripheral Bus (APB) which is part of the Advanced Microcontroller Bus Architecture (AMBA). It provides three key points:

1. The APB is optimized for low power consumption and reduced complexity by interfacing with low bandwidth peripherals. It uses a single clock edge to simplify timing analysis.

2. The APB bridge acts as the bus master, latching the address and controlling data transfer direction. It generates control signals to select the peripheral and indicate the transfer type (read/write).

3. APB peripherals use a simple interface, latching write data on the clock edge or enable signal. Reads return data when the peripheral is selected and transfer is

Axi protocol

Axi protocolAzad Mishra The document discusses Advanced eXtensible Interface (AXI), which is a third generation interface specification that is targeted at high performance systems. AXI uses separate address/control and data phases to improve performance. It supports burst transactions where only the start address is issued and multiple outstanding addresses can be in flight simultaneously. AXI consists of five channels to separate read and write operations. Simulation results showed that AXI provides higher throughput than older AMBA interfaces, though older interfaces may have lower latency in some cases. AXI's standardization and flexibility make it useful for integrating IP cores.

Axi

AxiVinchipsytm Vlsitraining The document discusses the Advanced eXtensible Interface (AXI) bus. AXI is a high-performance interface that supports high clock frequencies and burst transactions. It separates address/control and data phases and allows for multiple outstanding addresses. AXI consists of five channels for read/write address, data, and responses. It provides benefits like increased throughput and flexibility over older interfaces. Some limitations are burst size constraints and overhead from separate channels.

Axi

AxiAzad Mishra The document describes the Advanced eXtensible Interface (AXI) which is a high-performance interface used in system-on-chip (SoC) designs. AXI supports separate address/control and data phases to improve performance. It allows burst-based transactions where only the start address is issued and multiple outstanding addresses can be in flight simultaneously. AXI includes features like different burst types, cache support, protection units, error handling, and unaligned transfers to enhance system performance.

axi protocol

axi protocolAzad Mishra The AXI protocol specification describes an advanced bus architecture with burst-based transactions using separate address/control and data phases over independent channels. It supports features like out-of-order transaction completion, exclusive access for atomic operations, cache coherency, and a low power interface. The AXI protocol is commonly used in System-on-Chip designs for high performance embedded processors and peripherals.

Verification of amba axi bus protocol implementing incr and wrap burst using ...

Verification of amba axi bus protocol implementing incr and wrap burst using ...eSAT Journals Abstract This paper describes the development of verification environment for AMBA AXI (Advanced Extensible Interface) protocol using

System Verilog. AXI supports high performance, high-frequency system designs. It is an On-Chip communication protocol. It is

suitable for high-bandwidth and high frequency designs with minimal delays. It provides flexibility in the implementation of

interconnect architectures and avoid use of complex bridges. It is backward-compatible with existing AHB and APB interfaces.

The key features of the AXI protocol are that it consists of separate address, control and data phases. It support unaligned data

transfers using byte strobes. It requires only start address to be issued in a burst-based transaction. It has separate read and write

data channels that provide low-cost Direct Memory Access (DMA). This paper is aimed at the verification of various burst type

transaction (INCR and WRAP) of the AXI bus protocol and the Verification Environment is built using System Verilog coding[1].

Keywords: AMBA AXI, INCR, Wrap Burst, System Verilog

Axi protocol

Axi protocolRohit Kumar Pathak AXI is an on-chip, point to point communication protocol. It is used as a high-performance bus in various IP or SoC Systems. It is used for connecting high-performance processors with memory.

Design and Implementation of Axi-Apb Bridge based on Amba 4.0

Design and Implementation of Axi-Apb Bridge based on Amba 4.0ijsrd.com ARM introduced the Advanced Microcontroller Bus Architecture (AMBA) 4.0 specifications in March 2010, which includes Advanced eXtensible Interface (AXI) 4.0. AMBA bus protocol has become the de facto standard SoC bus. That means more and more existing IPs must be able to communicate with AMBA 4.0 bus. Based on AMBA 4.0 bus, we designed an Intellectual Property (IP) core of Advanced Peripheral Bus (APB) bridge, which translates the AXI4.0-lite transactions into APB 4.0 transactions. The bridge provides an interface between the high-performance AXI bus and low-power APB domain.

AHB To APB BRIDGE.pptx

AHB To APB BRIDGE.pptxGuckChick The document describes the AHB to APB bridge which is used to bridge communication between low bandwidth peripherals on the APB bus and high bandwidth devices on the AHB bus. The AHB to APB bridge acts as an AHB slave and provides an interface between the high-speed AHB and low-power APB. It buffers address, controls and data from the AHB and drives the APB peripherals, returning data and response signals to the AHB. The bridge performs data transfer from AHB to APB for write cycles and from APB to AHB for read cycles.

Amba axi 29 3_2015

Amba axi 29 3_2015kiemnhatminh The Amba AXI protocol enables high-bandwidth and low-latency interconnect between IP blocks through separate address/control and data channels that support burst-based transactions, out-of-order completion, and register slices for high-frequency operation. It uses two-way handshaking on channels and supports various burst types including incrementing, wrapping, and fixed bursts through start addresses and calculated transfer addresses.

Ral by pushpa

Ral by pushpa Pushpa Yakkala UVM RAL is an object-oriented model for registers inside the design. To access these design registers, UVM RAL provides ready-made base classes and APIs

AMBA AHB 5

AMBA AHB 5SUNODH GARLAPATI AMBA AHB is a bus interface suitable for high-performance synthesizable designs. It defines the interface between components, such as masters, interconnects, and slaves.

AMBA 5 COHERENT HUB INTERFACE.pptx

AMBA 5 COHERENT HUB INTERFACE.pptxSairam Chebrolu CHI is an evolution of the ACE protocol and part of the AMBA architecture. It was designed to improve performance and scalability for applications in mobile, networking, automotive and data center systems. CHI uses a layered architecture with protocol, network and link layers. It supports coherency across processor clusters and memory with topologies like ring, mesh and crossbar. Key nodes include request nodes, home nodes and subordinate nodes. The system address map routes transactions between nodes using unique node IDs.

UVM Methodology Tutorial

UVM Methodology TutorialArrow Devices UVM is a standardized methodology for verifying complex IP and SOC in the semiconductor industry. UVM is an Accellera standard and developed with support from multiple vendors Aldec, Cadence, Mentor, and Synopsys. UVM 1.0 was released on 28 Feb 2011 which is widely accepted by verification Engineer across the world. UVM has evolved and undergone a series of minor releases, which introduced new features.

UVM provides the standard structure for creating test-bench and UVCs. The following features are provided by UVM

• Separation of tests from test bench

• Transaction-level communication (TLM)

• Sequences

• Factory and configuration

• Message reporting

• End-of-test mechanism

• Register layer

Amba bus

Amba busrohitlinux The AMBA specification defines standards for on-chip communication in microcontrollers. It includes three bus standards: Advanced High-performance Bus (AHB) for high bandwidth communication, Advanced System Bus (ASB) and Advanced Peripheral Bus (APB) for lower bandwidth peripherals. The objectives are to facilitate right-first-time development, be technology independent, encourage modular design, and minimize infrastructure. A typical system has the CPU and memory on the high-performance AHB, with peripherals on the lower-bandwidth APB, connected via a bridge.

Amba presentation2

Amba presentation2Rashi Aggarwal AMBA AHB 2.0 is an open standard interconnect specification that defines the Advanced High-performance Bus (AHB) for connecting functional blocks in system-on-a-chip (SoC) designs. The AHB supports high-clock frequency and high-performance for system modules. It uses a multi-layer architecture as a crossbar switch between masters and slaves, allowing parallel links to support peak bandwidth without increasing frequency. The AHB is a single-channel, shared bus that defines read, write, burst and error response transfers along with associated control signals.

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoC

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoCRabindranath Tagore University, Bhopal This document describes a proposed Direct Memory Access controller (DMAC) architecture that is compliant with the Advanced Microcontroller Bus Architecture (AMBA) specification. The DMAC uses AMBA High-Performance Bus (AHB) and Advanced Peripheral Bus (APB) standards. It contains an AHB slave, APB master, and APB master module to allow parallel operations on the AHB and APB buses. The DMAC supports multi-channel operations, channel chaining, and uses an arbitration mechanism to prioritize channel access. It utilizes dual clock domains with an asynchronous FIFO and pulse synchronization for communications between domains.

AMBA3.0 james_20110801

AMBA3.0 james_20110801James Chang The document describes the AXI (Advanced eXtensible Interface) bus specification. AXI uses separate address/control and data phases with 5 independent channels - read address, write address, read data, write data, and write response. It supports burst-based transactions and out-of-order transaction completion. Register slices can be inserted to increase latency and maximize frequency. AXI defines signals for address, data, strobes, IDs, valid/ready handshaking and more to enable flexible on-chip interconnects.

Ad

More Related Content

What's hot (20)

AMBA 2.0 PPT

AMBA 2.0 PPTNirav Desai This document describes the implementation of an Advanced High Performance Bus (AHB) protocol using Verilog. It discusses the key components and signals of the AHB, including masters, slaves, arbiters, decoders, request/grant protocols, and pipelined transactions. It also provides RTL diagrams and simulation results for the arbiter, decoder, and multiplexer modules. The goal is to develop a synthesizable Verilog model of the AHB to allow easy addition of new blocks and improve bus efficiency through pipelined transactions.

Ambha axi

Ambha axiHARINATH REDDY Advanced eXtensible Interface (AXI), part of the ARM Advanced Microcontroller Bus Architecture (AMBA3) (AXI3) and 4 (AXI4) specifications.

AXI Protocol.pptx

AXI Protocol.pptxYazan Yousef A presentation about the AXI protocol includes all the signal description and explanation referred to the AXI specification

AMBA Ahb 2.0

AMBA Ahb 2.0Akhil Srivastava This document describes the Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB) 2.0 specification. It details features of AHB such as burst transfers, split transactions, and single-cycle bus master handover. It also explains typical components in an AMBA AHB system including masters, slaves, arbitration, and bus operation with different transfer types.

AMBA_APB_pst

AMBA_APB_pstBynaboina Krishna This document discusses the Advanced Peripheral Bus (APB) which is part of the Advanced Microcontroller Bus Architecture (AMBA). It provides three key points:

1. The APB is optimized for low power consumption and reduced complexity by interfacing with low bandwidth peripherals. It uses a single clock edge to simplify timing analysis.

2. The APB bridge acts as the bus master, latching the address and controlling data transfer direction. It generates control signals to select the peripheral and indicate the transfer type (read/write).

3. APB peripherals use a simple interface, latching write data on the clock edge or enable signal. Reads return data when the peripheral is selected and transfer is

Axi protocol

Axi protocolAzad Mishra The document discusses Advanced eXtensible Interface (AXI), which is a third generation interface specification that is targeted at high performance systems. AXI uses separate address/control and data phases to improve performance. It supports burst transactions where only the start address is issued and multiple outstanding addresses can be in flight simultaneously. AXI consists of five channels to separate read and write operations. Simulation results showed that AXI provides higher throughput than older AMBA interfaces, though older interfaces may have lower latency in some cases. AXI's standardization and flexibility make it useful for integrating IP cores.

Axi

AxiVinchipsytm Vlsitraining The document discusses the Advanced eXtensible Interface (AXI) bus. AXI is a high-performance interface that supports high clock frequencies and burst transactions. It separates address/control and data phases and allows for multiple outstanding addresses. AXI consists of five channels for read/write address, data, and responses. It provides benefits like increased throughput and flexibility over older interfaces. Some limitations are burst size constraints and overhead from separate channels.

Axi

AxiAzad Mishra The document describes the Advanced eXtensible Interface (AXI) which is a high-performance interface used in system-on-chip (SoC) designs. AXI supports separate address/control and data phases to improve performance. It allows burst-based transactions where only the start address is issued and multiple outstanding addresses can be in flight simultaneously. AXI includes features like different burst types, cache support, protection units, error handling, and unaligned transfers to enhance system performance.

axi protocol

axi protocolAzad Mishra The AXI protocol specification describes an advanced bus architecture with burst-based transactions using separate address/control and data phases over independent channels. It supports features like out-of-order transaction completion, exclusive access for atomic operations, cache coherency, and a low power interface. The AXI protocol is commonly used in System-on-Chip designs for high performance embedded processors and peripherals.

Verification of amba axi bus protocol implementing incr and wrap burst using ...

Verification of amba axi bus protocol implementing incr and wrap burst using ...eSAT Journals Abstract This paper describes the development of verification environment for AMBA AXI (Advanced Extensible Interface) protocol using

System Verilog. AXI supports high performance, high-frequency system designs. It is an On-Chip communication protocol. It is

suitable for high-bandwidth and high frequency designs with minimal delays. It provides flexibility in the implementation of

interconnect architectures and avoid use of complex bridges. It is backward-compatible with existing AHB and APB interfaces.

The key features of the AXI protocol are that it consists of separate address, control and data phases. It support unaligned data

transfers using byte strobes. It requires only start address to be issued in a burst-based transaction. It has separate read and write

data channels that provide low-cost Direct Memory Access (DMA). This paper is aimed at the verification of various burst type

transaction (INCR and WRAP) of the AXI bus protocol and the Verification Environment is built using System Verilog coding[1].

Keywords: AMBA AXI, INCR, Wrap Burst, System Verilog

Axi protocol

Axi protocolRohit Kumar Pathak AXI is an on-chip, point to point communication protocol. It is used as a high-performance bus in various IP or SoC Systems. It is used for connecting high-performance processors with memory.

Design and Implementation of Axi-Apb Bridge based on Amba 4.0

Design and Implementation of Axi-Apb Bridge based on Amba 4.0ijsrd.com ARM introduced the Advanced Microcontroller Bus Architecture (AMBA) 4.0 specifications in March 2010, which includes Advanced eXtensible Interface (AXI) 4.0. AMBA bus protocol has become the de facto standard SoC bus. That means more and more existing IPs must be able to communicate with AMBA 4.0 bus. Based on AMBA 4.0 bus, we designed an Intellectual Property (IP) core of Advanced Peripheral Bus (APB) bridge, which translates the AXI4.0-lite transactions into APB 4.0 transactions. The bridge provides an interface between the high-performance AXI bus and low-power APB domain.

AHB To APB BRIDGE.pptx

AHB To APB BRIDGE.pptxGuckChick The document describes the AHB to APB bridge which is used to bridge communication between low bandwidth peripherals on the APB bus and high bandwidth devices on the AHB bus. The AHB to APB bridge acts as an AHB slave and provides an interface between the high-speed AHB and low-power APB. It buffers address, controls and data from the AHB and drives the APB peripherals, returning data and response signals to the AHB. The bridge performs data transfer from AHB to APB for write cycles and from APB to AHB for read cycles.

Amba axi 29 3_2015

Amba axi 29 3_2015kiemnhatminh The Amba AXI protocol enables high-bandwidth and low-latency interconnect between IP blocks through separate address/control and data channels that support burst-based transactions, out-of-order completion, and register slices for high-frequency operation. It uses two-way handshaking on channels and supports various burst types including incrementing, wrapping, and fixed bursts through start addresses and calculated transfer addresses.

Ral by pushpa

Ral by pushpa Pushpa Yakkala UVM RAL is an object-oriented model for registers inside the design. To access these design registers, UVM RAL provides ready-made base classes and APIs

AMBA AHB 5

AMBA AHB 5SUNODH GARLAPATI AMBA AHB is a bus interface suitable for high-performance synthesizable designs. It defines the interface between components, such as masters, interconnects, and slaves.

AMBA 5 COHERENT HUB INTERFACE.pptx

AMBA 5 COHERENT HUB INTERFACE.pptxSairam Chebrolu CHI is an evolution of the ACE protocol and part of the AMBA architecture. It was designed to improve performance and scalability for applications in mobile, networking, automotive and data center systems. CHI uses a layered architecture with protocol, network and link layers. It supports coherency across processor clusters and memory with topologies like ring, mesh and crossbar. Key nodes include request nodes, home nodes and subordinate nodes. The system address map routes transactions between nodes using unique node IDs.

UVM Methodology Tutorial

UVM Methodology TutorialArrow Devices UVM is a standardized methodology for verifying complex IP and SOC in the semiconductor industry. UVM is an Accellera standard and developed with support from multiple vendors Aldec, Cadence, Mentor, and Synopsys. UVM 1.0 was released on 28 Feb 2011 which is widely accepted by verification Engineer across the world. UVM has evolved and undergone a series of minor releases, which introduced new features.

UVM provides the standard structure for creating test-bench and UVCs. The following features are provided by UVM

• Separation of tests from test bench

• Transaction-level communication (TLM)

• Sequences

• Factory and configuration

• Message reporting

• End-of-test mechanism

• Register layer

Amba bus

Amba busrohitlinux The AMBA specification defines standards for on-chip communication in microcontrollers. It includes three bus standards: Advanced High-performance Bus (AHB) for high bandwidth communication, Advanced System Bus (ASB) and Advanced Peripheral Bus (APB) for lower bandwidth peripherals. The objectives are to facilitate right-first-time development, be technology independent, encourage modular design, and minimize infrastructure. A typical system has the CPU and memory on the high-performance AHB, with peripherals on the lower-bandwidth APB, connected via a bridge.

Amba presentation2

Amba presentation2Rashi Aggarwal AMBA AHB 2.0 is an open standard interconnect specification that defines the Advanced High-performance Bus (AHB) for connecting functional blocks in system-on-a-chip (SoC) designs. The AHB supports high-clock frequency and high-performance for system modules. It uses a multi-layer architecture as a crossbar switch between masters and slaves, allowing parallel links to support peak bandwidth without increasing frequency. The AHB is a single-channel, shared bus that defines read, write, burst and error response transfers along with associated control signals.

Viewers also liked (18)

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoC

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoCRabindranath Tagore University, Bhopal This document describes a proposed Direct Memory Access controller (DMAC) architecture that is compliant with the Advanced Microcontroller Bus Architecture (AMBA) specification. The DMAC uses AMBA High-Performance Bus (AHB) and Advanced Peripheral Bus (APB) standards. It contains an AHB slave, APB master, and APB master module to allow parallel operations on the AHB and APB buses. The DMAC supports multi-channel operations, channel chaining, and uses an arbitration mechanism to prioritize channel access. It utilizes dual clock domains with an asynchronous FIFO and pulse synchronization for communications between domains.

AMBA3.0 james_20110801

AMBA3.0 james_20110801James Chang The document describes the AXI (Advanced eXtensible Interface) bus specification. AXI uses separate address/control and data phases with 5 independent channels - read address, write address, read data, write data, and write response. It supports burst-based transactions and out-of-order transaction completion. Register slices can be inserted to increase latency and maximize frequency. AXI defines signals for address, data, strobes, IDs, valid/ready handshaking and more to enable flexible on-chip interconnects.

I2 c protocol

I2 c protocolAzad Mishra The document discusses the I2C protocol, which uses just two bidirectional serial data lines (SDA and SCL) to allow multiple devices to communicate on the same bus. It supports synchronous communication at various speeds up to 5 Mbps. Devices are addressed using 7- or 10-bit addresses. Data is transferred in bytes, with start and stop conditions defining the beginning and end of each transmission. All data transitions must occur when the clock signal SCL is low.

SystemVerilog Assertions verification with SVAUnit - DVCon US 2016 Tutorial

SystemVerilog Assertions verification with SVAUnit - DVCon US 2016 TutorialAmiq Consulting This document provides an overview of SystemVerilog Assertions (SVAs) and the SVAUnit framework for verifying SVAs. It begins with an introduction to SVAs, including types of assertions and properties. It then discusses planning SVA development, such as identifying design characteristics and coding guidelines. The document outlines implementing SVAs and using the SVAUnit framework, which allows decoupling SVA definition from validation code. It provides an example demonstrating generating stimuli to validate an AMBA APB protocol SVA using SVAUnit. Finally, it summarizes SVAUnit's test API and features for error reporting and test coverage.

AXI Introduction

AXI IntroductionJason Boutselis The document discusses Axi International, a company that engineers and manufactures automated fuel maintenance systems and products to help customers maintain clean and reliable fuel wherever it is used or stored. Axi works with customers in various industries to create innovative solutions that extend engine life and improve fuel quality through automated filtration, polishing, sampling, and testing of fuel. Their goal is to educate customers on the ongoing changes in fuel production and delivery to ensure optimal engine performance and minimize downtime and costs associated with contaminated fuel.

Presentation apb 2015 perdir

Presentation apb 2015 perdirService Academique d'Information et d'Orientation Présentation de la procédure APB 2015 pour les équipes éducatives et les personnels de direction

RESUME_VISHNU_PRIYA

RESUME_VISHNU_PRIYAVishnu Priya V. Vishnu Priya is seeking a career as an ASIC verification engineer. She has a Post Graduate Diploma in VLSI Design & Technology from Industrial Training and Research Institute in Bangalore. She has skills in hardware languages like Verilog and SystemVerilog, verification methodology like UVM, and software languages like C. She has experience with EDA tools like Cadence and projects involving RTL coding, verification environments, and FSM design. Her education includes a B.Tech in ECE from Narayana Engineering College.

memcached Binary Protocol in a Nutshell

memcached Binary Protocol in a NutshellToru Maesaka Presentation on the upcoming Binary Protocol in memcached 1.3

This presentation covers how we can benefit from the binary protocol and how it actually works.

Delays in verilog

Delays in verilogJITU MISTRY Delays in Verilog allow modeling of timing aspects like propagation delays. There are different types of delays depending on the design approach - gate level modeling uses rise, fall, and turn-off delays while dataflow modeling uses assignment delays on nets. Behavioral modeling supports regular delays before assignments, intra-assignment delays after the equals sign, and zero delays to ensure last execution. Sequential and parallel blocks also control statement ordering.

Design and Implementation of AMBA ASB APB Bridge

Design and Implementation of AMBA ASB APB BridgeManu BN The 32 bit AMBA ASB APB Bridge provides an interface between the Advanced System Bus (ASB) and the Advanced Peripheral Bus (APB). It inserts wait states for a burst of read or write transfers when the ASB must wait for the APB. The bridge is designed to respond to transaction requests from the currently enabled ASB master. The ASB transactions are converted into APB transactions. APB peripherals do not need a clock input as the APB access is timed with a strobe signal generated by the ASB to APB bridge interface. The AMBA ASB APB Bridge is modeled using Verilog HDL and validated on SPARTAN 3E and the results are visualized on ChipScope Pro.

The design is also published in IEEE Xplore Link:

http://ieeeexplore.info/xpl/articleDetails.jsp?tp=&arnumber=6825442&queryText%3Dmanu+b.n

system verilog

system verilogVinchipsytm Vlsitraining The document describes a SystemVerilog verification methodology that includes assertion-based verification, coverage-driven verification, constrained random verification, and use of scoreboards and checkers. It outlines the verification flow from design specifications through testbench development, integration and simulation, and discusses techniques like self-checking test cases, top-level and block-level environments, and maintaining bug reports.

Mac protocols of adhoc network

Mac protocols of adhoc networkshashi712 The document discusses several MAC protocols for ad hoc networks including MACA, MACAW, and PAMAS. MACA uses RTS and CTS packets to avoid collisions but does not provide ACK. MACAW is a revision of MACA that includes ACK. It significantly increases throughput but does not fully solve hidden and exposed terminal problems. PAMAS uses a separate signaling channel for RTS-CTS and a data channel. It allows nodes to power down transceivers when not transmitting to save energy.

Mac protocols

Mac protocolsAnuj Gupta The document discusses several IEEE 802 standards for local and metropolitan area networks. It describes the purpose of IEEE 802 standards to define physical network interfaces and the lowest three layers of the network architecture. It provides details on some famous IEEE 802 standards including 802.2 (LLC), 802.3 (Ethernet), 802.4 (Token Bus), 802.5 (Token Ring), 802.6 (DQDB), and 802.11 (Wireless LAN). It then focuses on explaining the Ethernet, Token Bus and Token Ring standards in more depth including their frame formats and other specifications.

Track 3 session 4 - st dev con 2016 - sensortile

Track 3 session 4 - st dev con 2016 - sensortileST_World ST Developers Conference 2016 - Sensor Tile - Integrated Development Platform - Sensing, Processing and BLE connectivity

Track 1 session 4 - st dev con 2016 - mems piezo actuators

Track 1 session 4 - st dev con 2016 - mems piezo actuatorsST_World This presentation discusses piezoelectric MEMS actuators using thin film piezoelectric materials. It begins with an introduction to piezoelectricity and discusses lead zirconate titanate (PZT) as the most commonly used piezoelectric material. The presentation then covers the processing of thin film PZT, including sol-gel deposition and patterning techniques. Several applications of piezoelectric MEMS actuators are presented, including inkjet printheads, autofocus camera lenses, micropumps, and ultrasonic transducers. The presentation concludes by discussing opportunities for piezoelectric energy harvesting and ST's role in commercializing thin film piezo MEMS technology.

UVM TUTORIAL;

UVM TUTORIAL;Azad Mishra The document provides an overview of the UVM configuration database and how it is used to store and access configuration data throughout the verification environment hierarchy. Key points include: the configuration database mirrors the testbench topology; it uses a string-based key system to store and retrieve entries in a hierarchical and scope-controlled manner; and the automatic configuration process retrieves entries during the build phase and configures component fields.

Top 10 protocol interview questions with answers

Top 10 protocol interview questions with answersgracemartinez012 In this file, you can ref interview materials for protocol such as, protocol situational interview, protocol behavioral interview, protocol phone interview, protocol interview thank you letter, protocol interview tips …

Handy Culture Deck v1.0

Handy Culture Deck v1.0Handy The Handy Culture Deck provides an inside look at the uniquely Handy company and culture we are building to achieve our mission. It outlines the things we believe at Handy and the ways we try to live up to them.

Interested joining the team at Handy and changing the world? Visit handy.com/careers

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoC

Design and Implementation of an Advanced DMA Controller on AMBA-Based SoCRabindranath Tagore University, Bhopal

Ad

Similar to APB protocol v1.0 (20)

APB2SPI.pptx

APB2SPI.pptxSandeepkumarRangala The document describes the design and implementation of an APB to SPI converter using Verilog HDL. The converter allows for the transfer of data from the parallel APB protocol to the serial SPI protocol, handling the conversion between clock domains. Key components include status and control registers, a shifter logic to convert data to serial, a baud rate generator, and asynchronous FIFOs to buffer transmission and reception of data. The converter acts as an interface between the APB and SPI protocols.

AMBA 2.0

AMBA 2.0Mayankprajapati29 Advance Microcontroller Bus Architecture(AMBA).

this is a advance bus architecture. it is defined by ARM.

all the content is taken from http://infocenter.arm.com/ website.

AMBA Advanced High-performance Bus (AHB) protocol

AMBA Advanced High-performance Bus (AHB) protocolfavecol712 This presentation provides a detailed overview of the AMBA High-performance Bus (AHB) protocol. It covers AHB architecture, transfer types, bus states, pipelining concepts, error handling, timing diagrams, and real-world use cases. Additionally, it includes comparisons of AHB with APB for a better understanding of bus hierarchies. Perfect for beginners and intermediate learners aiming to strengthen their knowledge of AMBA protocols in SoC design and verification.

VLSI DESIGN OF AMBA BASED AHB2APB BRIDGE

VLSI DESIGN OF AMBA BASED AHB2APB BRIDGEVLSICS Design The Advanced Microcontroller Bus Architecture (AMBA) is an open System-on-Chip bus protocol for highperformance buses to communicate with low-power devices. In the AMBA Advanced High Performance bus (AHB) a system bus is used to connect a processor, a DSP, and high-performance memory controllers where as the AMBA Advanced Peripheral Bus (APB) is used to connect (Universal Asynchronous Receiver Transmitter) UART. It also contains a Bridge, which connects the AHB and APB buses. Bridges are standard bus-to-bus interfaces that allow IPs connected to different buses to communicate with each other in a standardized way. So AHB2APB bridge is designed, implemented using VERILOG tool and tested using Verilog testbench and is reported in this paper. A synthesizable RTL code of a complex interface

bridge between AHB and APB is developed and known as AHB2APB Bridge. The simulated AHB2APB Bridge results are promising and can be further tested for its verstality by writing a verification program using UVM in future.

VLSI DESIGN OF AMBA BASED AHB2APB BRIDGE

VLSI DESIGN OF AMBA BASED AHB2APB BRIDGEVLSICS Design The Advanced Microcontroller Bus Architecture (AMBA) is an open System-on-Chip bus protocol for highperformance

buses to communicate with low-power devices. In the AMBA Advanced High Performance bus (AHB) a system bus is used to connect a processor, a DSP, and high-performance memory controllers where as the AMBA Advanced Peripheral Bus (APB) is used to connect (Universal Asynchronous Receiver Transmitter) UART. It also contains a Bridge, which connects the AHB and APB buses. Bridges are standard bus-to-bus interfaces that allow IPs connected to different buses to communicate with each other in a standardized way. So AHB2APB bridge is designed, implemented using VERILOG tool and tested using Verilog testbench and is reported in this paper. A synthesizable RTL code of a complex interface

bridge between AHB and APB is developed and known as AHB2APB Bridge. The simulated AHB2APB Bridge results are promising and can be further tested for its verstality by writing a verification program using UVM in future.

VLSI DESIGN OF AMBA BASED AHB2APBBRIDGE

VLSI DESIGN OF AMBA BASED AHB2APBBRIDGEVLSICS Design The Advanced Microcontroller Bus Architecture (AMBA) is an open System-on-Chip bus protocol for highperformance buses to communicate with low-power devices. In the AMBA Advanced High Performance bus (AHB) a system bus is used to connect a processor, a DSP, and high-performance memory controllers where as the AMBA Advanced Peripheral Bus (APB) is used to connect (Universal Asynchronous Receiver Transmitter) UART. It also contains a Bridge, which connects the AHB and APB buses. Bridges are standard bus-to-bus interfaces that allow IPs connected to different buses to communicate with each other in a standardized way. So AHB2APB bridge is designed, implemented using VERILOG tool and tested using Verilog testbench and is reported in this paper. A synthesizable RTL code of a complex interface bridge between AHB and APB is developed and known as AHB2APB Bridge. The simulated AHB2APB Bridge results are promising and can be further tested for its verstality by writing a verification program using UVM in future.

IRJET- Design and Verification of APB Protocol by using System Verilog and Un...

IRJET- Design and Verification of APB Protocol by using System Verilog and Un...IRJET Journal This document describes the design and verification of an AMBA APB protocol using System Verilog and Universal Verification Methodology (UVM). It begins with an introduction to AMBA and the APB bus protocol. The APB design is created in Verilog and consists of an APB bridge/master and APB slaves. The design is then verified using System Verilog and UVM testbenches. Simulation waveforms and UVM reports show the data written by the master is correctly read by the slave, indicating the APB protocol is functioning as intended.

8051d

8051dSenthil Kumar The instruction set of the 8051 microcontroller supports 8-bit operations and direct bit manipulation well suited for control applications. It has 256 instructions that use various addressing modes including register, direct, indirect, immediate, relative, and others. The instruction set includes arithmetic, logical, data transfer, boolean, and branching instructions. Conditional jumps and operations on individual bits allow for efficient programming of control flow and logic.

8051d.ppt microcontroller instruction set summary

8051d.ppt microcontroller instruction set summaryanushkayadav3011 8051d.ppt microcontroller instruction set summary

mod 3-1.pptx

mod 3-1.pptxlekha349785 The ARM processor uses a 3-stage pipeline with fetch, decode, and execute stages. It has a register bank, barrel shifter, ALU, address register, data registers, and instruction decoder. In the 5-stage pipeline, the stages are fetch, decode, execute, buffer/data, and write-back. Data processing instructions use two operands from registers or immediates, while data transfer instructions compute a memory address. The core components are optimized for speed, including carry look-ahead adders and a crossbar barrel shifter. Control logic decodes instructions and controls the datapath. The coprocessor interface supports up to 16 coprocessors with private registers.

Universal synchronous asynchronous receiver transmitter(usart) and AtoD Coverter

Universal synchronous asynchronous receiver transmitter(usart) and AtoD CoverterTejas Shetye The document discusses the Universal Synchronous Asynchronous Receiver Transmitter (USART) and Analog-to-Digital Converter (ADC) components in PIC microcontrollers. It describes how USART can be configured for synchronous or asynchronous communication and the functions of its TXSTA and RCSTA registers. It also explains the steps for ADC conversion, including configuring the ADC module, selecting the input channel, starting conversion, and reading the result registers.

final

finalShahar Gefen The document describes the design and implementation of a CAN bus controller to enable reliable communication between nodes using the CAN protocol. It discusses the motivation for using CAN in embedded systems and provides details on the controller's architecture, which includes modules for CAN, APB interface, and interrupts. It also covers the controller's design flow from learning CAN and APB specifications to simulation, synthesis, and layout. The controller was synthesized at 100MHz with low area and power.

40120130406005

40120130406005IAEME Publication This document summarizes an article from the International Journal of Electronics and Communication Engineering & Technology that proposes a design for an efficient AXI2.0 to APB bridge. It begins with introductions to the AXI2.0 and APB protocols. It then describes the proposed bridge design, which uses asynchronous FIFOs to connect the different clock domains and resolve protocol mismatches. The design is implemented in VHDL and synthesized on a Xilinx Virtex 4 FPGA. Simulation results and the synthesis report are presented, showing the bridge utilizes a small amount of device resources.

Interfacing technique with 8085- ADC[0808]![Interfacing technique with 8085- ADC[0808]](https://cdn.slidesharecdn.com/ss_thumbnails/adc-160307140900-thumbnail.jpg?width=560&fit=bounds)

![Interfacing technique with 8085- ADC[0808]](https://cdn.slidesharecdn.com/ss_thumbnails/adc-160307140900-thumbnail.jpg?width=560&fit=bounds)

![Interfacing technique with 8085- ADC[0808]](https://cdn.slidesharecdn.com/ss_thumbnails/adc-160307140900-thumbnail.jpg?width=560&fit=bounds)

![Interfacing technique with 8085- ADC[0808]](https://cdn.slidesharecdn.com/ss_thumbnails/adc-160307140900-thumbnail.jpg?width=560&fit=bounds)

Interfacing technique with 8085- ADC[0808]Guhan k The document describes the ADC0808 analog to digital converter chip. It has an 8-channel multiplexer that selects which analog input signal to convert to digital. The conversion process takes 64 clock cycles to complete. The chip outputs the digital conversion result on 8 pins and has control signal pins for start, clock, output enable and end of conversion notification. It converts analog voltages to 8-bit digital numbers for use by digital devices like microprocessors.

Fpga implemented ahb protocol

Fpga implemented ahb protocoliaemedu This document describes the implementation of an Advanced High-performance Bus (AHB) protocol using an FPGA. It provides an overview of the AHB protocol which allows for communication between multiple bus masters and slaves. The AHB protocol supports features like split transactions, burst transfers, and arbitration. The document implements an AHB system with three masters and four slaves on an FPGA. It presents waveform results showing the arbiter prioritizing requests from multiple masters and handling the transfer of data between masters and slaves using the AHB protocol. In conclusion, the AHB protocol implemented on an FPGA provides benefits like avoiding deadlocks, minimizing lost resources, and adding flexibility.

First seminar

First seminarNishant Srivastav This document describes the design of a 16-bit microprocessor using VHDL. It includes descriptions of the components of the processor like the ALU, registers, control unit and their functions. It explains the design flow from writing VHDL code to synthesis and simulation. The overall operation of the completed microprocessor is also summarized.

Interfacing rs232

Interfacing rs232PRADEEP The document discusses interfacing RS232 with microcontrollers. RS232 uses asynchronous communication and the UART (Universal Asynchronous Receiver/Transmitter) to interface with microcontrollers like the ATmel 89C51. The MAX232 IC is used as a driver to interface RS232 with other devices. Baud rates for communication are set using special function registers in the microcontroller that control the serial port. The baud rate can be doubled by setting the SMOD bit in the PCON register. Data is transmitted by storing it in the serial buffer and cleared the transmit interrupt flag, and received by reading the serial buffer when the receive interrupt flag is set. Functions make it easier to send and receive multiple characters of data through the

Ad

Recently uploaded (20)

Take this ppt refference and give content on mahindra commitment to sustainab...

Take this ppt refference and give content on mahindra commitment to sustainab...kochars428 Take this ppt refference and give content on mahindra commitment to sustainability, CGSR and corporate governance

Are you Transitioning or Refining Now..?

Are you Transitioning or Refining Now..?Gregory Vigneaux If the question is, "How will society survive wildfires moving forward?" wildfire-adapted communities are a promising answer. According to the Fire Adapted Communities Learning Network, "A fire-adapted community is a community that understands its risk and takes action before, during, and after the fire in order for their community to be more resilient to wildfire." If fire-adapted communities have the potential to be effective, how are they brought into being? The prior introduces the very question this theoretical discussion-based lecture seeks to explore on April 30th at 10 a.m. - 11:30:00 p.m. MDT.

Former Hotshot and winner of the National Park Service's Fuels and Ecology Award for Promoting Fire-Adapted Human Communities, Gregory Vigneaux draws on years of research to examine two modes of wildfire-adapted community change: transitions and refining the present. Attendees will be introduced to the unique pathways, dynamics, and concepts that shape each mode. The talk begins by discussing place before discussing how place is dwelled in and what that means for change.

Through theoretical exploration, participants will be introduced to language and insights for a better understanding of the changes they hope to effect and explore whether a different approach might be more effective. This discussion does not address physical fire adaptation, such as creating defensible space and home hardening, but instead examines processes of change.

This event is tailored for anyone interested in creating wildfire-adapted communities. For example, fire-adapted practitioners and stakeholders, community groups, fire mitigation experts, insurers, emergency managers, government fire officials, nonprofits, private organizations, and others. The talk provides valuable insights into community change processes around wildfire risk.

Oversized Off White Pulka Dot Cotton Shirt

Oversized Off White Pulka Dot Cotton ShirtZNKL.in Elevate your wardrobe with this chic abstract print shirt. Featuring a collared V-neck and button-down front, this versatile piece offers a relaxed fit with long sleeves. The striking black and white pattern adds a modern touch to any outfit, perfect for both casual and semi-formal occasions.

𝗗𝗲𝘀𝗶𝗴𝗻𝗶𝗻𝗴 𝗳𝗼𝗿 𝗮𝗹𝗹: 𝗜𝗻𝗰𝗹𝘂𝘀𝗶𝘃𝗲 𝗣𝗿𝗮𝗰𝘁𝗶𝗰𝗲 𝗳𝗼𝗿 𝗕𝗲𝘁𝘁𝗲𝗿 𝗘𝘅𝗽𝗲𝗿𝗶𝗲𝗻𝗰𝗲𝘀

𝗗𝗲𝘀𝗶𝗴𝗻𝗶𝗻𝗴 𝗳𝗼𝗿 𝗮𝗹𝗹: 𝗜𝗻𝗰𝗹𝘂𝘀𝗶𝘃𝗲 𝗣𝗿𝗮𝗰𝘁𝗶𝗰𝗲 𝗳𝗼𝗿 𝗕𝗲𝘁𝘁𝗲𝗿 𝗘𝘅𝗽𝗲𝗿𝗶𝗲𝗻𝗰𝗲𝘀Friends of Figm a, Sydney 𝗗𝗲𝘀𝗶𝗴𝗻𝗶𝗻𝗴 𝗳𝗼𝗿 𝗮𝗹𝗹: 𝗜𝗻𝗰𝗹𝘂𝘀𝗶𝘃𝗲 𝗣𝗿𝗮𝗰𝘁𝗶𝗰𝗲 𝗳𝗼𝗿 𝗕𝗲𝘁𝘁𝗲𝗿 𝗘𝘅𝗽𝗲𝗿𝗶𝗲𝗻𝗰𝗲𝘀 @ The University of Sydney - 1st March 2025

AR.AKSHAYA PAMBALATH-PORTFOLIOFINAL_.pdf

AR.AKSHAYA PAMBALATH-PORTFOLIOFINAL_.pdfakshayap23 This portfolio showcases a curated selection of academic, professional, and conceptual architectural projects, highlighting a comprehensive design approach that merges aesthetics, functionality, and contextual sensitivity. Each project demonstrates proficiency in design development, technical detailing, and presentation, along with strong command over industry-standard software tools.From large-scale urban planning proposals to intimate interior spaces, the portfolio reflects a commitment to sustainability, innovation, and user-centered design. The work embodies a balance between conceptual clarity and technical precision, aiming to address real-world challenges through thoughtful architectural solutions.Included are detailed drawings, 3D visualizations, physical models, and process sketches that collectively represent a holistic design process.Throughout the portfolio, you'll find,Conceptual Development: Idea generation, site studies, and early-stage diagrams that lay the foundation for each project.

Architectural Drawings: Detailed plans, sections, elevations, and construction details showcasing clarity and precision.

3D Visualizations and Renderings: Realistic and conceptual renderings that communicate spatial atmosphere and design intent.

Physical Models and Process Work: Documentation of physical prototypes and iterative design processes that illustrate hands-on exploration.

Technical and Software Proficiency: Demonstration of skills in software such as AutoCAD, Rhino, Revit, SketchUp, Adobe Creative Suite, Lumion, and others.

Modern Gradient Startup Pitch Deck PowerPoint Presentation and Google Slides ...

Modern Gradient Startup Pitch Deck PowerPoint Presentation and Google Slides ...SlidesBrain Modern Gradient Startup Pitch Deck – PowerPoint Presentation and Google Slides Themes

Are you ready to take your startup idea to the next level? 🚀 Whether you're preparing for an investor meeting, a product launch, or simply want to create an unforgettable first impression, our Modern Gradient Startup Pitch Deck is designed just for you.

At SlidesBrain, we believe that your presentation is more than just slides – it's your story, your brand, and your future. This Startup Pitch Deck features clean, bold, and modern gradient designs that instantly capture attention. It’s fully editable and compatible with PowerPoint and Google Slides, giving you the flexibility to customize it to your needs.

With the perfect blend of professional structure and creative design, this deck is ideal for startups across industries — tech, wellness, e-commerce, SaaS, and more. From problem statements to solutions, team slides to financial projections, every layout you need is covered.

🎨 What You’ll Get:

Stunning gradient backgrounds for a modern and sleek look

Investor-focused layouts to pitch your idea effectively

100% editable elements — fonts, colors, icons, and images

Compatible with both PowerPoint and Google Slides

Fully customizable according to your brand identity

✨ Whether you are preparing for a seed funding round, Series A, or even just showcasing your concept, this pitch deck template helps you tell your story in a way that’s visually compelling and professionally impressive.

More About SlidesBrain:

At SlidesBrain, we provide high-quality, beautifully crafted Free PowerPoint Templates for professionals, startups, entrepreneurs, and creators who want to stand out.

Need something even more unique? Our Custom Design Services are available to help you build tailor-made presentations that perfectly reflect your brand's essence.

📩 Want to impress your audience? Let's work together!

Contact us for custom solutions or download free templates at [email protected].

#StartupPitchDeck #ModernPresentation #SlidesBrain #GradientDesign #PitchDeckDesign #PowerPointTemplates #GoogleSlidesThemes #StartupPresentation #InvestorPitch #BusinessPresentation #CustomPresentationDesign #TechStartup #StartupSuccess #Entrepreneurship #FreePowerPointTemplates #PresentationInspiration #SlidesDesign #InvestorDeck #CustomSlides #DeckDesign #SaaSStartup #StartupBranding #SeedFundingPitch #BusinessGrowth #SlidesBrainServices #PresentationTemplates

Minimalist Pitch Deck by slide Slidesgo.pptx

Minimalist Pitch Deck by slide Slidesgo.pptxESTEFANOANDREYGARCIA changas changas changelion y changela

The Irrational City | Unseen Forces of Placemaking

The Irrational City | Unseen Forces of PlacemakingLeanne Munyori What if cities weren’t built for how people live—but for how planners think they should?

We explored Nairobi’s evolving urban form through the lens of behavioral economics and environmental psychology. The Irrational City challenges conventional planning paradigms by revealing how emotion, perception, and cognitive bias shape how we experience and respond to the built environment.

Drawing from principles of irrational decision-making, place attachment, and choice architecture, this talk questions:

– Why do some places feel safe, others alienating?

– How does infrastructure influence behavior, intentionally or not?

– Can we design cities not just for function, but for feeling?

From expressways to the feauture park, Nairobi offers a live case study in how unconscious design decisions affect well-being, identity, and belonging. This presentation is for architects, planners, designers, and anyone curious about cities as emotional ecosystems—not just physical ones.

Venngage AI Infographic Generator- AI-powered visuals that turn your ideas in...

Venngage AI Infographic Generator- AI-powered visuals that turn your ideas in...Venngage AI Infographic Generator Venngage’s AI Infographic Generator helps you bring clarity to your content by turning plain text into visually compelling infographics—automatically. Designed with marketers and communicators in mind, it’s built to simplify complex messaging and speed up your workflow.

With just a short prompt, the AI understands your intent and creates a structured infographic that fits your content type—whether you’re outlining a process, comparing features, or mapping out a timeline. The tool selects fonts, icons, layouts, and visual hierarchy for you, taking care of the heavy lifting in seconds.

Once generated, you can fully customize the design to align with your brand—tweak colors, edit text, replace visuals, and adjust layout elements using a simple drag-and-drop editor. The tool supports different infographic styles, making it ideal for internal reports, client presentations, blog content, and social media graphics.

What makes it valuable for marketers?

- Eliminate bottlenecks in the content creation process

- Get campaign visuals and data summaries out faster

- Repackage written content into visuals that perform better on social and email

- Communicate insights clearly with clients and internal teams

Whether you're on a tight deadline or just want to simplify your storytelling, Venngage’s AI helps you create high-impact visuals without relying on a designer or starting from scratch.

Generate AI Infographics here: https://venngage.com/ai-tools/infographic-generator

19 Best B,u,y Verified Cash App Accounts

19 Best B,u,y Verified Cash App Accountshttps://sellsusa.com/product/buy-verified-cash-app-accounts/ https://sellsusa.com/product/buy-verified-cash-app-accounts/

Telegram:- @sellsusa

WhatsApp:- +1 (606) 264–0854

Email: [email protected])

Venngage AI Infographic Generator- AI-powered visuals that turn your ideas in...

Venngage AI Infographic Generator- AI-powered visuals that turn your ideas in...Venngage AI Infographic Generator

19 Best B,u,y Verified Cash App Accounts

19 Best B,u,y Verified Cash App Accountshttps://sellsusa.com/product/buy-verified-cash-app-accounts/

APB protocol v1.0

- 1. APB Protocol v 1.0 ● Introduction ● Transfers ● Operating States ● Signal Descriptions

- 2. Conventions This section describes the conventions that this specification uses: •Typographical ● Timing diagrams •Signals

- 3. Typographical ● This specification uses the following typographical conventions: ● Italic - Highlights important notes, introduces special terminology,denotes internal cross-references, and citations. ● Bold - Highlights interface elements, such as menu names. Denotes ARM processor signal names. Also used for terms in descriptive lists, where appropriate. ● Monospace - Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code. ● Monospace - Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

- 4. ●monospace italic - Denotes arguments to monospace text where the argument is to be replaced by a specific value. ●monospace bold - denotes language keywords when used outside example code. ●<and> - Angle brackets enclose replaceable terms for assembler syntax where they appear in code or code fragments. They appear in normal font in running text. For example: ● MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2> ● The Opcode_2 value selects which register is accessed.

- 7. Signals ● The signal conventions are: ● Signal level - The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means HIGH for active-HIGH signals and LOW for active- LOW signals. ● Prefix P - Denotes AMBA 3 APB signals. ● Suffix n - Denotes AXI, AHB, and AMBA 3 APB reset signals.

- 8. About the AMBA 3 APB ● The APB is part of the AMBA 3 protocol family. It provides a low cost interface that is optimized for minimal power consumption and reduced interface complexity. ● The APB interfaces to any peripherals that are low-bandwidth and do not require the high performance of a pipelined bus interface. The APB has unpipelined protocol. ● All signal transitions are only related to the rising edge of the clock to enable the integration of APB peripherals easily into any design flow. Every transfer takes at least two cycles. ● The APB can interface with the AMBA Advanced High-performance Bus Lite (AHB-Lite) and AMBA Advanced Extensible Interface (AXI). You can use it to provide access to the programmable control registers of peripheral devices.

- 9. Changes for AMBA 3 APB Protocol Specification v1.0 ● This version includes: ● A ready signal, PREADY, to extend an APB transfer. ● An error signal, PSLVERR, to indicate the failure of a transfer.

- 10. Transfers ● Write transfers ● Two types of write transfer are described in this section: ● With no wait states ● With wait states.

- 11. With no wait states

- 12. The write transfer starts with the address, write data, write signal and select signal all changing after the rising edge of the clock. The first clock cycle of the transfer is called the Setup phase. After the following clock edge the enable signal is asserted, PENABLE, and this indicates that the Access phase is taking place. The address, data and control signals all remain valid throughout the Access phase. The transfer completes at the end of this cycle. The enable signal, PENABLE, is deasserted at the end of the transfer. The select signal, PSELx, also goes LOW unless the transfer is to be followed immediately by another transfer to the same peripheral.

- 13. With wait states ● Figure shows how the PREADY signal from the slave can extend the transfer. During an Access phase, when PENABLE is HIGH, the transfer can be extended by driving PREADY LOW. The following signals remain unchanged for the additional cycles: ● address, PADDR ● write signal, PWRITE ● select signal, PSEL ● enable signal, PENABLE ● write data, PWDATA.

- 14. Write transfer with wait states

- 15. ● PREADY can take any value when PENABLE is LOW. This ensures that peripherals that have a fixed two cycle access can tie PREADY HIGH. ● NOTE - It is recommended that the address and write signals are not changed immediately after a transfer but remain stable until another access occurs. This reduces power consumption.

- 16. Read transfers ● Two types of read transfer are described in this section: ● With no wait states ● With wait states.

- 17. With no wait states Figure shows a read transfer. The timing of the address, write, select, and enable signals are as described in Write transfers on page 2-2. The slave must provide the data before the end of the read transfer

- 18. With wait states ● Figure shows how the PREADY signal can extend the transfer. The transfer is extended if PREADY is driven LOW during an Access phase. The protocol ensures that the following remain unchanged for the additional cycles: ● address, PADDR ● write signal, PWRITE ● select signal, PSEL ● enable signal, PENABLE. ● Figure shows that two cycles are added using the PREADY signal. However, you can add any number of additional cycles, from zero upwards.

- 20. Error response ● You can use PSLVERR to indicate an error condition on an APB transfer. Error conditions can occur on both read and write transactions. ● PSLVERR is only considered valid during the last cycle of an APB transfer, when PSEL, PENABLE, and PREADY are all HIGH ● It is recommended, but not mandatory, that you drive PSLVERR LOW when it is not being sampled. That is, when any of PSEL, PENABLE, or PREADY are LOW.

- 21. Error response contd.. ● Transactions that receive an error, might or might not have changed the state of the peripheral. This is peripheral-specific and either is acceptable. When a write transaction receives an error this does not mean that the register within the peripheral has not been updated. Read transactions that receive an error can return invalid data. There is no requirement for the peripheral to drive the data bus to all 0s for a read error. ● APB peripherals are not required to support the PSLVERR pin. This is true for both existing and new APB peripheral designs. Where a peripheral does not include this pin then the appropriate input to the APB bridge is tied LOW.

- 22. Write transfer ● Figure shows an example of a failing write transfer that completes with an error.

- 23. Read transfer ● A read transfer can also complete with an error response, indicating that there is no valid read data available. Figure 2-6 on page 2-7 shows a read transfer completing with an error response.

- 24. Mapping of PSLVERR ● When bridging: ● From AXI to APB An APB error is mapped back to RRESP/BRESP = SLVERR. This is achieved by mapping PSLVERR to the AXI signals RRESP[1] for reads and BRESP[1] for writes. ● From AHB to APB PSLVERR is mapped back to HRESP = ERROR for both reads and writes. This is ac

- 25. Operating States Figure shows the operational activity of the APB.

- 26. The state machine operates through the following states: ● IDLE - This is the default state of the APB. ● SETUP - When a transfer is required the bus moves into the SETUP state, where the appropriate select signal, PSELx, is asserted. The bus only remains in the SETUP state for one clock cycle and always moves to the ACCESS state on the next rising edge of the clock.

- 27. Contd.... ● ACCESS - The enable signal, PENABLE, is asserted in the ACCESS state. The address, write, select, and write data signals must remain stable during the transition from the SETUP to ACCESS state. Exit from the ACCESS state is controlled by the PREADY signal from the slave: 1 - If PREADY is held LOW by the slave then the peripheral bus remains in the ACCESS state. 2 - If PREADY is driven HIGH by the slave then the ACCESS state is exited and the bus returns to the IDLE state if no more transfers are required. Alternatively, the bus moves directly to the SETUP state if another transfer follows.

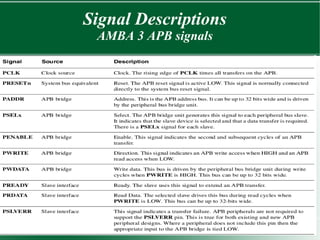

- 28. Signal Descriptions AMBA 3 APB signals

![Halstead’s_Software_Science_&_Putnam’s_Model[1].pptx](https://cdn.slidesharecdn.com/ss_thumbnails/halsteadssoftwarescienceputnamsmodel1-250502175814-4c85707e-thumbnail.jpg?width=560&fit=bounds)