Comp Arithmetic Basic.ppt

- 1. INTRODUCING COMPUTER ARCHITECTURE & SYSTEM SOFTWARE [For BCA 1stYear] Presented & Compiled By Abhijit Sarkar Asst. Professor Institute of Engineering & Management

- 2. Differentiating Computer Organization & Computer Architecture Computer Organization:- It study the way hardware components operate and the way they are connected together to form computer system. Computer Architecture:- It study the behavior of computer as seen by external user and performance enhancement strategy.

- 3. Basic Component of Computer

- 5. Von Neumann Architecture Model for designing and building computers, based on the following three characteristics: 1) The computer consists of four main sub-systems: Memory ALU (Arithmetic/Logic Unit) Control Unit Input/ Output System (I/O) 2) Program is stored in memory during execution along with instruction. (Stored Program Concept) 3) Program instructions are executed sequentially one at a time.

- 7. Bottlenecks of Von-Neumann Architecture Address modification scheme was inefficient. No instruction were provided for structured programming. Floating point arithmetic was not implemented. Less importance to I/O instruction. Programming logical & non-numeric problem was difficult.

- 12. 1’s-Complement To change the sign of a binary integer simply complement (invert) each bit. Example: 3 = 0011, – 3 = 1100

- 13. 2’s-Complement Add 1 to 1’s-complement representation. Some properties: Only one representation for 0 Exactly as many positive numbers as negative numbers Sign-magnitude 000 = +0 001 = +1 010 = +2 011 = +3 100 = - 0 101 = - 1 110 = - 2 111 = - 3 1’s complement 000 = +0 001 = +1 010 = +2 011 = +3 100 = - 3 101 = - 2 110 = - 1 111 = - 0 2’s complement 000 = +0 001 = +1 010 = +2 011 = +3 100 = - 4 101 = - 3 110 = - 2 111 = - 1 (Preferred) 000= -0

- 14. Integer Representation Positive Number:- Only have 0 & 1 to represent everything Positive numbers stored in binary e.g. 41=00101001 No minus sign +12 (8 bit register) 00001100

- 15. Integer Representation Negative Number:- -12 Left most bit is sign bit 0 means positive 1 means negative +18 = 00010010 -18 = 10010010 10001100(Signed Magnitude) 11110011(Signed 1’s Compliment) 11110100(Signed 2’s Compliment)

- 16. Fixed Point Representation Decimal point exist in a fixed place. .0011 [Fraction Number] 1100. [Integer Number]

- 17. Floating Point Representation Floating-point numbers allow an arbitrary number of decimal places to the right of the decimal point. For example: 0.5 0.25 = 0.125 They are often expressed in scientific notation. For example: 0.125 = 1.25 10-1 5,000,000 = 5.0 106

- 18. Floating Point Representation Numbers written in scientific notation have three components: Mantissa:- Signed fixed point number Exponent:- Position of decimal point 24.25 = 2.425 x 101 Mantissa = 2.425 Radix = 10 Exponent = 1

- 19. IEEE 754 The IEEE has established a standard for floating-point numbers Standard for floating point storage 32 and 64 bit standards The IEEE-754 single precision floating point standard uses an 8-bit exponent and a 23-bit significand. The IEEE-754 double precision standard uses an 11-bit exponent and a 52-bit significand.

- 20. IEEE 754 Biased Exponent:- Actual Exponent (Unbiased) Biased Exponent (Adding 127 to get all +ve values) 0 127 1 128 127 254 -127 0 -100 27

- 21. Revisiting Binary to Gray & Gray to Binary Conversion Gray Code is unit Distance code i.e. between two Successive codes the number of changes in bits = 1

- 22. Revisiting Gray to Binary Conversion Gray Code is unit Distance code i.e. between two Successive codes the number of changes in bits = 1

- 23. Revisiting Gray to Binary Conversion Example: Gray Code: g3 g2 g1 g0 = 1 0 0 1 then Binary Code: b3 b2 b1 b0 b3 = g3 = 1 b2 = b3 ⊕ g2 = 1 ⊕ 0 = 1 b1 = b2 ⊕ g1 = 1 ⊕ 0 = 1 b0 = b1 ⊕ g0 =1 ⊕ 1 = 0 ∴ Final Binary Code: 1 1 1 0

- 24. Revisiting Binary to Gray Conversion g3 = b3 g2 = b3 ⊕ b2 g1 = b2 ⊕ b1 g0 = b1 ⊕ b0

- 25. Revisiting Binary to Gray Conversion Binary Code: b3 b2 b1 b0 = 1 1 1 0 Gray Code: g3 g2 g1 g0 g3 = b3 = 1 g2 = b3 ⊕ b2 = 1 ⊕ 1 = 0 g1 = b2 ⊕ b1 = 1 ⊕ 1 = 0 g0 = b1 ⊕ b0 =1 ⊕ 0 = 1 ∴ Final Gray code: 1 0 0 1

- 26. Revisiting Binary - Gray Conversion

- 27. REPRESENTATION OF NUMBERS - POSITIONAL NUMBERS

- 28. CONVERSION OF BASES Decimal to Base R number Base R to Decimal Conversion V(A) = ak Rk A = an-1 an-2 an-3 … a0 . a-1 … a-m (736.4)8 = 7 x 82 + 3 x 81 + 6 x 80 + 4 x 8-1 = 7 x 64 + 3 x 8 + 6 x 1 + 4/8 = (478.5)10 (110110)2 = ... = (54)10 (110.111)2 = ... = (6.785)10 (F3)16 = ... = (243)10 - Separate the number into its integer and fraction parts and convert each part separately. - Convert integer part into the base R number → successive divisions by R and accumulation of the remainders. - Convert fraction part into the base R number → successive multiplications by R and accumulation of integer digits

- 29. EXAMPLE Convert 41.687510 to base 2. Integer = 41 41 20 1 10 0 5 0 2 1 1 0 0 1 Fraction = 0.6875 0.6875 x 2 1.3750 x 2 0.7500 x 2 1.5000 x 2 1.0000 (41)10 = (101001)2 (0.6875)10 = (0.1011)2 (41.6875)10 = (101001.1011)2 Convert (63)10 to base 5: (223)5 Convert (1863)10 to base 8: (3507)8 Convert (0.63671875)10 to hexadecimal: (0.A3)16 Exercise

- 30. Binary Addition Rules for binary addition are: 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 0 with 1 to carry for the next column

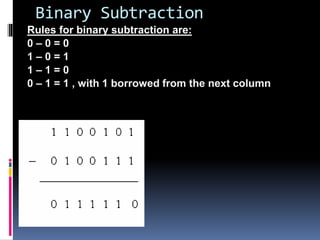

- 31. Binary Subtraction Rules for binary subtraction are: 0 – 0 = 0 1 – 0 = 1 1 – 1 = 0 0 – 1 = 1 , with 1 borrowed from the next column

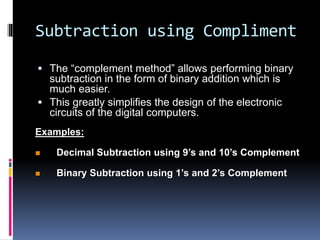

- 32. Subtraction using Compliment The “complement method” allows performing binary subtraction in the form of binary addition which is much easier. This greatly simplifies the design of the electronic circuits of the digital computers. Examples: Decimal Subtraction using 9’s and 10’s Complement Binary Subtraction using 1’s and 2’s Complement

- 33. Subtraction using 1’s/9’s Compliment Algorithm for M-N:- Step -1:- Add M to 1’s compliment/ 9’s compliment of N. Step-2:- If end carry occurs, add 1 to LSD Step-3:- If end carry doesn’t occur, take 1’s/ 9’s compliment of result and place a (-ve) sign before it. Example:- M=1100, N=0001 1100+1110=1 | 1010+1=1011 (Result)

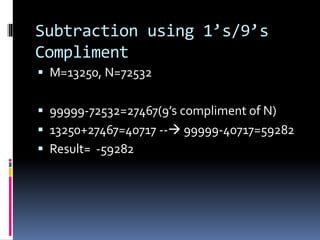

- 34. Subtraction using 1’s/9’s Compliment M=13250, N=72532 99999-72532=27467(9’s compliment of N) 13250+27467=40717 -- 99999-40717=59282 Result= -59282

- 35. Subtraction using 2’s/10’s Compliment Algorithm for M-N:- Step-1:-Add M to 2’s compliment/ 10’s compliment of N. Step-2:- If end carry occurs, discard it. Step-2:- If end carry doesn’t occur, take 2’s/ 10’s compliment of result and place a (-ve) sign in front of it. Example:- M=1000, N=1110 1000+0010=1010(No end carry) So, 2’s compliment of 1010=0110 -0110 (Result)

- 36. Subtraction using 2’s/10’s Compliment M=3250, N=72532 M-N=? 99999-72532=27467+1=27468 (10’s compliment of N) 03250+27468=30718 (No end carry) 10’s compliment of 30718=99999- 30718=69281+1=69282 Result= -69282

- 37. Subtraction using Complement Exercise Calculate the following binary Subtraction: 11101.101 – 1011.11 using direct subtraction, 1’s and 2’s compliment.

- 38. Subtraction using Complement Exercise Calculate the following binary Subtraction: 11001.10010 – 11101.00111 using direct subtraction, 1’s and 2’s compliment & verify it in decimal.

- 39. Design Hardware Bit by Bit Adding two bits: a b half_sum carry_out 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 Half-adder circuit

- 40. Full-Adder

- 41. Full-Adder

- 42. Serial Adder Circuits operate with N clock cycles for N bit addition

- 43. Serial Adder

- 44. Parallel Adder Drawback:- Circuit involves delay, the carry propagation time is the major speed limiting factor Circuits operate with 1 clock cycles for N bit addition

- 45. Carry Look ahead Adder Gi is known as the carry Generate signal since a carry (Ci+1) is generated whenever Gi =1, regardless of the input carry (Ci). Pi is known as the carry propagate signal since whenever Pi =1, the input carry is propagated to the output carry, i.e., Ci+1. = Ci Computing the values of Pi and Gi only depend on the input operand bits Ai & Bi

- 46. Carry Look ahead Adder-Logic

- 47. Carry Look ahead Adder-Circuit

- 48. Binary Incrementer The binary Incrementer increases the value stored in a register by ‘1’. For this, it simply adds ‘1’ to the existing value stored in a register. It is made by cascading ‘n’ half adders for ‘n’ number of bits i.e. the storage capacity of the register to be incremented. Hence, a 4-bit binary incrementer requires 4 cascaded half adder circuits.

- 49. Binary Incrementer The increment microoperation adds one to a number in a register. This increment can be done independent of a register by the means of a combinational circuit called BINARY INCREMENTER.

- 51. Adder-Subtractor Circuit The addition and subtraction operations can be combined into one common circuit called BINARY ADDER-SUBTRACTOR. This can be done by including an exclusive- OR gate with each full adder in binary adder.

- 56. Binary Multiplication The multiplication of two binary numbers can be carried out in the same manner as the decimal multiplication. Unlike decimal multiplication, only two values are generated as the outcome of multiplying the multiplication bit by 0 or 1 in the binary multiplication.These values are either 0 or 1. The binary multiplication can also be considered as repeated binary addition.Therefore, the binary multiplication is performed in conjunction with the binary addition operation.

- 58. Booth’s Multiplication- Logic Consider a positive multiplier consisting of a block of 1’s surrounded by 0’s. For example, 00111110.The product is given by:- M x “00111110” = M x (25 + 24 + 23 + 22 + 21) = M x 62 , where M is the multiplicand. The number of operations can be reduced to two by rewriting the same as:- M x “ 01000000 – 00000010” = M x (26 – 21) = M x 62 In fact, it can be shown that any sequence of 1's in a binary number can be broken into the difference of two binary numbers:

- 59. Booth’s Multiplication M-N is equivalent to M+2’s compliment of N e.g. M=1000 N=0001 M-N=? 2’s compliment of N (N’+1)=1110+1=1111 M+N’+1= 1000 (+)1111 1 0111

- 62. Booth’s Multiplication Illustration (Exercise) Multiply -9 x -14 (Using Booth’s Multiplication)

- 63. Multiply +11 x -13(Using Booth’s Multiplication)

- 64. Multiplying +11 and -13 +11->01011 ->BR -13 -> 11101 ->1 0010+1 -> 10011->QR BR’+1 ->10100+1 -> 10101 Result -> 010001110+1 ->010001111 -> - 143

- 65. Multiplying -6 and +9 -6 -> 10110 ->1 1001+1 -> 11010 ->BR +9 -> 01001 ->QR BR’+1 -> 00101 +1 -> 00110 Result -> 000110101+1 ->000110110 -> - 54

- 68. Dividing 14 / 3 Remainder -> +0010 ->+2 Quotient -> +0100 -> +4 +14 -> 1110 -> E (dividend) +3 -> 0011 -> D (divisor) Restoring Division

- 70. Non-restoring division Illustration Dividend (Q) = 101110, ie 46 Divisor (M) = 010111, ie 23.

- 72. Revisiting Combinational Circuit: Decoder Accepts a value and decodes it Output corresponds to value of n inputs Used in selecting memory location as well as chip. Consists of: Inputs (n) Outputs (2n , numbered from 0 2n - 1) Selectors / Enable (active high or active low)

- 73. Revisiting Combinational Circuit: Decoder Decoder Expansion (3:8 using two 2:4 decoders)

- 74. Revisiting Combinational Circuit: Encoder Perform the inverse operation of a decoder 2n (or less) input lines and n output lines

- 75. Priority Encoder Compresses multiple binary inputs into a smaller number of outputs. If two or more inputs are given at the same time, the input having the highest priority will take precedence.

- 76. Revisiting Combinational Circuit: Multiplexer A multiplexer can use addressing bits to select one of several input bits to be the output. A selector chooses a single data input and passes it to the MUX output. It has one output selected at a time.

- 77. Revisiting Combinational Circuit: Cascading Multiplexer

- 78. Revisiting Combinational Circuit: Demultiplexer Given an input line and a set of selection lines, the demultiplexer will direct data from input to a selected output line. An example of a 1-to-4 demultiplexer:

- 79. 4-bit Circuit to perform Add, Add with carry, Subtraction, Subtraction with borrow, Transfer, Increment and Decrement

- 80. 4-bit Circuit to perform Add, Add with carry, Subtraction, Subtraction with borrow, Transfer, Increment and Decrement S1 S0 Cin Y Ouput D =A+Y+Cin Operation 0 0 0 B D=A+B Add 0 0 1 B D=A+B+1 Add with Carry 0 1 0 B’ D=A+B’ Subtraction 0 1 1 B’ D=A+B’+1 Subtraction with borrow 1 0 0 0 D=A Transfer (A R) 1 0 1 0 D=A+1 Increment of A 1 1 0 1 D=A-1 Decrement of A

![INTRODUCING COMPUTER

ARCHITECTURE & SYSTEM

SOFTWARE

[For BCA 1stYear]

Presented & Compiled By

Abhijit Sarkar

Asst. Professor

Institute of Engineering & Management](https://image.slidesharecdn.com/comparithmeticbasic-230722082747-ab288da7/85/Comp-Arithmetic-Basic-ppt-1-320.jpg)

![Fixed Point Representation

Decimal point exist in a fixed place.

.0011 [Fraction Number]

1100. [Integer Number]](https://image.slidesharecdn.com/comparithmeticbasic-230722082747-ab288da7/85/Comp-Arithmetic-Basic-ppt-16-320.jpg)