Csc1401 lecture03 - computer arithmetic - arithmetic and logic unit (alu)

6 likes4,665 views

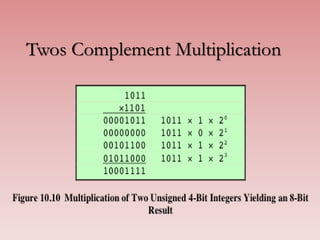

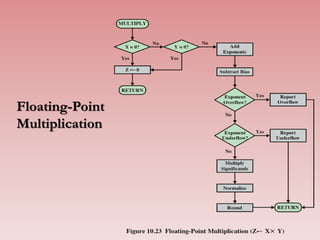

1. The document discusses various ways that computers represent integers and floating point numbers for processing, including unsigned, sign magnitude, one's complement, two's complement, and biased representations for integers. It also discusses the typical components of the floating point format including the sign, exponent, and significand. 2. Key aspects of arithmetic operations like addition, subtraction, multiplication, and division are described for different number representations. The two's complement system is highlighted as the most common approach used in computers due to its simplicity. 3. Standards like IEEE 754 are covered which define floating point standards to help ensure portability of numeric programs across systems.

1 of 44

Downloaded 207 times

Ad

Recommended

Computer arithmetic

Computer arithmeticBalakrishna Chowdary All the data about computer arithmetic .. i searched for it in slide share but no result.. so i made it for u guys..

General register organization (computer organization)

General register organization (computer organization)rishi ram khanal This document discusses the organization of a CPU and its registers. It includes tables that encode the register selection fields and ALU operations. It also provides examples of micro-operations for the CPU, showing the register selections, ALU operations, and control words. Key registers discussed include the accumulator, instruction register, address register, and program counter.

Multiplication algorithm

Multiplication algorithmGaurav Subham Booth's multiplication algorithm multiplies two signed binary numbers in two's complement notation. It was invented by Andrew Donald Booth in 1950. The algorithm inspects two bits of the multiplier at a time, and either adds, subtracts, or leaves unchanged the partial product depending on whether the bits are 10, 01, or the same. It shifts the partial product and multiplier arithmeticly to the right after each step to inspect the next bits.

Booth’s algorithm.(a014& a015)

Booth’s algorithm.(a014& a015)Piyush Rochwani This document provides an overview of Booth's algorithm for multiplying signed and unsigned integers. It begins with an introduction and history, noting that the algorithm was invented by Andrew Donald Booth in 1950. It then explains the key points of Booth's algorithm through a flow chart and examples. For unsigned integers, it uses fewer additions/subtractions than other methods by conditionally adding or subtracting the multiplicand. For signed integers, it first converts them to unsigned using 2's complement before applying the same process.

Instruction Set Architecture

Instruction Set ArchitectureDilum Bandara The document discusses instruction set architecture (ISA), which is part of computer architecture related to programming. It defines the native data types, instructions, registers, addressing modes, and other low-level aspects of a computer's operation. Well-known ISAs include x86, ARM, MIPS, and RISC. A good ISA lasts through many implementations, supports a variety of uses, and provides convenient functions while permitting efficient implementation. Assembly language is used to program at the level of an ISA's registers, instructions, and execution order.

1. Arithmetic Operations - Addition and subtraction of signed numbers.pptx

1. Arithmetic Operations - Addition and subtraction of signed numbers.pptxJEEVANANTHAMG6 1) The document discusses arithmetic operations in computer architecture including addition, subtraction, and representation of signed integers.

2) It describes fixed point number representation using signed and unsigned integers, and one's complement representation for negative numbers.

3) The full adder circuit is explained as accepting two input bits and a carry bit to generate a sum and carry out bit, and its truth table is shown.

Input Output Organization

Input Output OrganizationKamal Acharya The document discusses various methods for input/output (IO) in computer systems, including IO interfaces, programmed IO, interrupt-initiated IO, direct memory access (DMA), and input-output processors (IOPs). It describes how each method facilitates the transfer of data between the CPU, memory, and external IO devices.

Division algorithm

Division algorithmSnehalataAgasti Division algorithm involves dividing a dividend by a divisor to obtain a quotient and remainder. There are two types of division algorithms: restoring division and non-restoring division. Non-restoring division was demonstrated by dividing 8 by 3 in binary form using a divisor of 0011, a minuend of 1000, and a running difference stored in a accumulator to iteratively obtain the quotient 1000 and keep the division process non-negative.

Two’s complement

Two’s complementmayannpolisticoLNU Two's complement representation allows binary arithmetic on signed integers to yield the correct results. Positive numbers are represented as simple binary, while negative numbers are the binary complement of the corresponding positive number. The most significant bit indicates the sign, with 0 being positive and 1 being negative. To calculate the two's complement of a number, invert and add 1 to its binary representation. Two's complement arithmetic follows the same rules as binary arithmetic. Overflow occurs when adding two numbers of the same sign yields a result with the opposite sign.

Floating point representation

Floating point representationmissstevenson01 Real numbers can be stored using floating point representation, which separates a real number into three parts: a sign bit, exponent, and mantissa. The exponent indicates the power of the base 10 that the mantissa is multiplied by. Common standards like IEEE 754 define single and double precision formats that allocate more bits for higher precision at the cost of range. Summarizing a floating point number involves determining the exponent by shifting the decimal, converting the number to a leading digit mantissa, and writing the sign, exponent, and mantissa based on the specified precision format.

Booths algorithm for Multiplication

Booths algorithm for MultiplicationVikas Yadav Booths algorithm for Multiplication with flowchart for easy understanding with explained suitable examples.

Register transfer language

Register transfer languageSanjeev Patel Register transfer language is used to describe micro-operation transfers between registers. It represents the sequence of micro-operations performed on binary information stored in registers and the control that initiates the sequences. A register is a group of flip-flops that store binary information. Information can be transferred between registers using replacement operators and control functions. Common bus systems using multiplexers or three-state buffers allow efficient information transfer between multiple registers by selecting one register at a time to connect to the shared bus lines. Memory transfers are represented by specifying the memory word selected by the address in a register and the data register involved in the transfer.

Instruction codes and computer registers

Instruction codes and computer registersSanjeev Patel The document discusses instruction codes and computer registers. Instruction codes are made up of an opcode and address that tell the computer what operation to perform. Computer registers store important data and instructions, including the program counter, address register, instruction register, temporary register, data register, accumulator, input register, and output register. These registers perform functions like holding memory operands, instructions, temporary data, addresses, and input/output characters.

Logic microoperations

Logic microoperationsNitesh Singh The document describes logic microoperations which are the basic logic functions performed on binary variables. It lists 16 logic microoperations corresponding to the 16 possible functions of two binary variables. These include operations like AND, OR, XOR, complement etc. It then discusses the hardware implementation of some logic microoperations using a multiplexer. It further explains various applications of logic microoperations like selective set, clear, complement etc. and how they can manipulate individual bits in a register. Shift microoperations and an arithmetic logic shift unit are also summarized.

Binary Arithmetic

Binary Arithmeticgavhays The document discusses binary arithmetic operations including addition, subtraction, multiplication, and division. It provides examples and step-by-step explanations of how to perform each operation in binary. For addition and subtraction, it explains the rules and concepts like carry bits and two's complement. For multiplication, it describes the shift-and-add method. And for division, it outlines the long division approach of shift-and-subtract in binary.

Pipelining and vector processing

Pipelining and vector processingKamal Acharya This slide contain the description about the various technique related to parallel Processing(vector Processing and array processor), Arithmetic pipeline, Instruction Pipeline, SIMD processor, Attached array processor

Instruction code

Instruction codeDr. Abhineet Anand The document discusses different types of instruction codes used in computers. It explains that instruction codes contain operation codes and operands. The operation code specifies the operation to be performed, like addition, subtraction, etc. The operands specify the data on which the operation will be performed, which can be stored in memory or registers. The document outlines three main types of instruction codes - memory reference instructions, register reference instructions, and input-output instructions. It describes the format of each type of instruction and how they are interpreted by the computer.

Binary Arithmetic Operations

Binary Arithmetic OperationsDigital System Design In this slide we have discussed, different arithmetic operations like addition, subtraction, multiplication and division for binary numbers. Addition and subtraction operation is achieved using one's complement and two's complement number system.

Signed Binary Numbers

Signed Binary Numberspyingkodi maran The document discusses different methods for representing signed binary numbers:

1) Sign-magnitude notation represents positive and negative numbers by using the most significant bit to indicate the sign (0 for positive, 1 for negative) and the remaining bits for the magnitude.

2) One's complement represents negative numbers by inverting all bits of the positive number.

3) Two's complement, the most common method, represents negative numbers by inverting all bits and adding 1 to the result. This allows simple addition to perform subtraction.

Computer organisation -morris mano

Computer organisation -morris manovishnu murthy This document outlines the syllabus for a course on computer organization and architecture. The syllabus covers 10 units: 1) introduction to computers, 2) register transfer and micro-operations, 3) computer arithmetic, 4) programming the basic computer, 5) central processing unit organization, 6) input-output organization, 7) memory organization, 8) parallel processing, 9) vector processing, and 10) multiprocessors. Key topics include Von Neumann architecture, computer generations, instruction execution, registers, buses, arithmetic logic units, assembly language, and memory hierarchies. References for the course are also provided.

Input output interface

Input output interfaceChrist University This document provides an overview of input/output interfaces in 3 paragraphs. It discusses how I/O devices communicate differently than internal storage due to differences in operation, data transfer rates, word formats, and peripheral operating modes. It describes how interface modules connect I/O devices like keyboards, displays, printers and storage to the I/O bus and processor. Finally, it provides an example of an I/O interface unit that uses control and status registers to facilitate communication between a CPU and I/O device over control, data and status lines.

Bit pair recoding

Bit pair recodingBasit Ali Bit-pair recoding is a technique that halves the maximum number of additions needed for multiplication by recoding the multiplier bits into pairs. It works by selecting the multiplicand (the number being multiplied) based on the values of bit pairs in the multiplier. For each bit pair, the selection table indicates which multiplicand (the regular value or the negative value) to use. This allows multiplication to be performed with only n/2 additions, where n is the number of bits in the multiplier.

Microprogrammed Control Unit

Microprogrammed Control UnitPreethiSureshkumar1 (Ref : Computer System Architecture by Morris Mano 3rd edition) : Microprogrammed Control unit, micro instructions, micro operations, symbolic and binary microprogram.

Assembly Language

Assembly LanguageIbrahimcommunication Al Ani Assembly language is a low-level programming language that corresponds directly to a processor's machine language instructions. It uses symbolic codes that are assembled into machine-readable object code. Assembly languages are commonly used when speed, compact code size, or direct hardware interaction is important. Assemblers translate assembly language into binary machine code that can be directly executed by processors.

Register transfer language & its micro operations

Register transfer language & its micro operationsLakshya Sharma The document discusses register transfer language and micro-operations in digital systems. It describes (1) how register transfer language can be used to describe the sequence of micro-operations involved in any computer function, (2) the four main types of micro-operations - register transfer, arithmetic, logic, and shift micro-operations, giving examples of each, and (3) how register transfers and bus transfers are represented in register transfer language.

Binary arithmetic

Binary arithmeticElizabeth de Leon Aler Binary arithmetic is essential for digital computers and systems. It involves adding, subtracting, multiplying, and dividing binary numbers using basic rules. Signed binary numbers represent positive and negative values using sign-magnitude, 1's complement, and 2's complement methods. Arithmetic operations on signed binary numbers follow rules for handling the sign bit and complement representations.

Chapter 1 digital systems and binary numbers

Chapter 1 digital systems and binary numbersMohammad Bashartullah Digital systems represent information using discrete binary values of 0 and 1 rather than continuous analog values. Binary numbers use a base-2 numbering system with place values that are powers of 2. There are various number systems like decimal, binary, octal and hexadecimal that use different number bases and represent the same number in different ways. Complements are used in binary arithmetic to perform subtraction by adding the 1's or 2's complement of a number. The 1's complement is obtained by inverting all bits, while the 2's complement is obtained by inverting all bits and adding 1.

Computer architecture data representation

Computer architecture data representationAnil Pokhrel This document discusses various methods of data representation in digital systems, including number systems, data types, and encoding of numeric values. It covers binary, decimal, and floating point representation, as well as techniques for representing negative numbers like signed magnitude, 1's complement, and 2's complement. Error detection codes like parity bits are also introduced as a way to detect errors during data transmission. Key topics include binary conversion of decimal numbers, floating point representation using mantissa and exponent, overflow detection, and even/odd parity generation.

Computer arithmetic

Computer arithmeticBuddhans Shrestha This document discusses computer arithmetic and hardware for signed-magnitude addition and subtraction. It contains the following key points:

1) Computer arithmetic refers to basic operations like addition, subtraction, multiplication, and division performed with operands. It provides examples of signed-magnitude addition and subtraction rules and the hardware used to perform these operations.

2) The hardware for signed-magnitude addition and subtraction includes an A register, B register, complementer, parallel adder, and mode control. It performs the operations by setting the registers and control signals.

3) Algorithms for signed 2's complement addition and subtraction are also presented, showing how numbers are added or subtracted based on their relative magnitudes stored in the registers.

Chapter 05 computer arithmetic

Chapter 05 computer arithmeticIIUI The document discusses computer arithmetic and binary numbers. It begins by explaining why computers use the binary number system instead of decimal. The key reasons are that electronic components can only represent two states, binary is simpler for circuit design, and arithmetic is possible with binary. The document then covers the basic arithmetic operations of addition, subtraction, multiplication, and division in binary. It provides rules for each operation and examples to illustrate how to perform the calculations in binary. Finally, it discusses complementary subtraction and the additive method for multiplication and division.

Ad

More Related Content

What's hot (20)

Two’s complement

Two’s complementmayannpolisticoLNU Two's complement representation allows binary arithmetic on signed integers to yield the correct results. Positive numbers are represented as simple binary, while negative numbers are the binary complement of the corresponding positive number. The most significant bit indicates the sign, with 0 being positive and 1 being negative. To calculate the two's complement of a number, invert and add 1 to its binary representation. Two's complement arithmetic follows the same rules as binary arithmetic. Overflow occurs when adding two numbers of the same sign yields a result with the opposite sign.

Floating point representation

Floating point representationmissstevenson01 Real numbers can be stored using floating point representation, which separates a real number into three parts: a sign bit, exponent, and mantissa. The exponent indicates the power of the base 10 that the mantissa is multiplied by. Common standards like IEEE 754 define single and double precision formats that allocate more bits for higher precision at the cost of range. Summarizing a floating point number involves determining the exponent by shifting the decimal, converting the number to a leading digit mantissa, and writing the sign, exponent, and mantissa based on the specified precision format.

Booths algorithm for Multiplication

Booths algorithm for MultiplicationVikas Yadav Booths algorithm for Multiplication with flowchart for easy understanding with explained suitable examples.

Register transfer language

Register transfer languageSanjeev Patel Register transfer language is used to describe micro-operation transfers between registers. It represents the sequence of micro-operations performed on binary information stored in registers and the control that initiates the sequences. A register is a group of flip-flops that store binary information. Information can be transferred between registers using replacement operators and control functions. Common bus systems using multiplexers or three-state buffers allow efficient information transfer between multiple registers by selecting one register at a time to connect to the shared bus lines. Memory transfers are represented by specifying the memory word selected by the address in a register and the data register involved in the transfer.

Instruction codes and computer registers

Instruction codes and computer registersSanjeev Patel The document discusses instruction codes and computer registers. Instruction codes are made up of an opcode and address that tell the computer what operation to perform. Computer registers store important data and instructions, including the program counter, address register, instruction register, temporary register, data register, accumulator, input register, and output register. These registers perform functions like holding memory operands, instructions, temporary data, addresses, and input/output characters.

Logic microoperations

Logic microoperationsNitesh Singh The document describes logic microoperations which are the basic logic functions performed on binary variables. It lists 16 logic microoperations corresponding to the 16 possible functions of two binary variables. These include operations like AND, OR, XOR, complement etc. It then discusses the hardware implementation of some logic microoperations using a multiplexer. It further explains various applications of logic microoperations like selective set, clear, complement etc. and how they can manipulate individual bits in a register. Shift microoperations and an arithmetic logic shift unit are also summarized.

Binary Arithmetic

Binary Arithmeticgavhays The document discusses binary arithmetic operations including addition, subtraction, multiplication, and division. It provides examples and step-by-step explanations of how to perform each operation in binary. For addition and subtraction, it explains the rules and concepts like carry bits and two's complement. For multiplication, it describes the shift-and-add method. And for division, it outlines the long division approach of shift-and-subtract in binary.

Pipelining and vector processing

Pipelining and vector processingKamal Acharya This slide contain the description about the various technique related to parallel Processing(vector Processing and array processor), Arithmetic pipeline, Instruction Pipeline, SIMD processor, Attached array processor

Instruction code

Instruction codeDr. Abhineet Anand The document discusses different types of instruction codes used in computers. It explains that instruction codes contain operation codes and operands. The operation code specifies the operation to be performed, like addition, subtraction, etc. The operands specify the data on which the operation will be performed, which can be stored in memory or registers. The document outlines three main types of instruction codes - memory reference instructions, register reference instructions, and input-output instructions. It describes the format of each type of instruction and how they are interpreted by the computer.

Binary Arithmetic Operations

Binary Arithmetic OperationsDigital System Design In this slide we have discussed, different arithmetic operations like addition, subtraction, multiplication and division for binary numbers. Addition and subtraction operation is achieved using one's complement and two's complement number system.

Signed Binary Numbers

Signed Binary Numberspyingkodi maran The document discusses different methods for representing signed binary numbers:

1) Sign-magnitude notation represents positive and negative numbers by using the most significant bit to indicate the sign (0 for positive, 1 for negative) and the remaining bits for the magnitude.

2) One's complement represents negative numbers by inverting all bits of the positive number.

3) Two's complement, the most common method, represents negative numbers by inverting all bits and adding 1 to the result. This allows simple addition to perform subtraction.

Computer organisation -morris mano

Computer organisation -morris manovishnu murthy This document outlines the syllabus for a course on computer organization and architecture. The syllabus covers 10 units: 1) introduction to computers, 2) register transfer and micro-operations, 3) computer arithmetic, 4) programming the basic computer, 5) central processing unit organization, 6) input-output organization, 7) memory organization, 8) parallel processing, 9) vector processing, and 10) multiprocessors. Key topics include Von Neumann architecture, computer generations, instruction execution, registers, buses, arithmetic logic units, assembly language, and memory hierarchies. References for the course are also provided.

Input output interface

Input output interfaceChrist University This document provides an overview of input/output interfaces in 3 paragraphs. It discusses how I/O devices communicate differently than internal storage due to differences in operation, data transfer rates, word formats, and peripheral operating modes. It describes how interface modules connect I/O devices like keyboards, displays, printers and storage to the I/O bus and processor. Finally, it provides an example of an I/O interface unit that uses control and status registers to facilitate communication between a CPU and I/O device over control, data and status lines.

Bit pair recoding

Bit pair recodingBasit Ali Bit-pair recoding is a technique that halves the maximum number of additions needed for multiplication by recoding the multiplier bits into pairs. It works by selecting the multiplicand (the number being multiplied) based on the values of bit pairs in the multiplier. For each bit pair, the selection table indicates which multiplicand (the regular value or the negative value) to use. This allows multiplication to be performed with only n/2 additions, where n is the number of bits in the multiplier.

Microprogrammed Control Unit

Microprogrammed Control UnitPreethiSureshkumar1 (Ref : Computer System Architecture by Morris Mano 3rd edition) : Microprogrammed Control unit, micro instructions, micro operations, symbolic and binary microprogram.

Assembly Language

Assembly LanguageIbrahimcommunication Al Ani Assembly language is a low-level programming language that corresponds directly to a processor's machine language instructions. It uses symbolic codes that are assembled into machine-readable object code. Assembly languages are commonly used when speed, compact code size, or direct hardware interaction is important. Assemblers translate assembly language into binary machine code that can be directly executed by processors.

Register transfer language & its micro operations

Register transfer language & its micro operationsLakshya Sharma The document discusses register transfer language and micro-operations in digital systems. It describes (1) how register transfer language can be used to describe the sequence of micro-operations involved in any computer function, (2) the four main types of micro-operations - register transfer, arithmetic, logic, and shift micro-operations, giving examples of each, and (3) how register transfers and bus transfers are represented in register transfer language.

Binary arithmetic

Binary arithmeticElizabeth de Leon Aler Binary arithmetic is essential for digital computers and systems. It involves adding, subtracting, multiplying, and dividing binary numbers using basic rules. Signed binary numbers represent positive and negative values using sign-magnitude, 1's complement, and 2's complement methods. Arithmetic operations on signed binary numbers follow rules for handling the sign bit and complement representations.

Chapter 1 digital systems and binary numbers

Chapter 1 digital systems and binary numbersMohammad Bashartullah Digital systems represent information using discrete binary values of 0 and 1 rather than continuous analog values. Binary numbers use a base-2 numbering system with place values that are powers of 2. There are various number systems like decimal, binary, octal and hexadecimal that use different number bases and represent the same number in different ways. Complements are used in binary arithmetic to perform subtraction by adding the 1's or 2's complement of a number. The 1's complement is obtained by inverting all bits, while the 2's complement is obtained by inverting all bits and adding 1.

Computer architecture data representation

Computer architecture data representationAnil Pokhrel This document discusses various methods of data representation in digital systems, including number systems, data types, and encoding of numeric values. It covers binary, decimal, and floating point representation, as well as techniques for representing negative numbers like signed magnitude, 1's complement, and 2's complement. Error detection codes like parity bits are also introduced as a way to detect errors during data transmission. Key topics include binary conversion of decimal numbers, floating point representation using mantissa and exponent, overflow detection, and even/odd parity generation.

Viewers also liked (20)

Computer arithmetic

Computer arithmeticBuddhans Shrestha This document discusses computer arithmetic and hardware for signed-magnitude addition and subtraction. It contains the following key points:

1) Computer arithmetic refers to basic operations like addition, subtraction, multiplication, and division performed with operands. It provides examples of signed-magnitude addition and subtraction rules and the hardware used to perform these operations.

2) The hardware for signed-magnitude addition and subtraction includes an A register, B register, complementer, parallel adder, and mode control. It performs the operations by setting the registers and control signals.

3) Algorithms for signed 2's complement addition and subtraction are also presented, showing how numbers are added or subtracted based on their relative magnitudes stored in the registers.

Chapter 05 computer arithmetic

Chapter 05 computer arithmeticIIUI The document discusses computer arithmetic and binary numbers. It begins by explaining why computers use the binary number system instead of decimal. The key reasons are that electronic components can only represent two states, binary is simpler for circuit design, and arithmetic is possible with binary. The document then covers the basic arithmetic operations of addition, subtraction, multiplication, and division in binary. It provides rules for each operation and examples to illustrate how to perform the calculations in binary. Finally, it discusses complementary subtraction and the additive method for multiplication and division.

Chapter 03 arithmetic for computers

Chapter 03 arithmetic for computersBảo Hoang This document discusses computer arithmetic and floating point representation. It begins with an introduction to computer arithmetic and covers topics like addition, subtraction, multiplication, division and their algorithms. It then discusses floating point representation which uses scientific notation to represent real numbers. Key aspects covered include single and double precision formats, normalized and denormalized numbers, overflow and underflow, and biased exponent representation. Examples are provided to illustrate floating point addition and multiplication. The document also discusses floating point instructions in MIPS and the need for accurate arithmetic in floating point operations.

09 Arithmetic

09 ArithmeticJeanie Delos Arcos The document discusses computer arithmetic and floating point number representation. It covers:

1) The Arithmetic Logic Unit (ALU) performs calculations and can handle integers and floating point numbers using separate floating point units.

2) Integer numbers are represented using binary and two's complement allows for positive and negative numbers. Floating point numbers use a sign bit, significand, and exponent in normalized form to represent numbers with fractions.

3) Operations like addition, subtraction, multiplication, and division are performed on integers in the ALU and floating point numbers following standard algorithms while managing overflow and normalization.

09 arithmetic

09 arithmeticSher Shah Merkhel The document summarizes computer arithmetic and the arithmetic logic unit (ALU). It discusses:

1) The ALU handles integer and floating point calculations. It may have a separate floating point unit.

2) There are different methods for representing integers like sign-magnitude and two's complement. Two's complement is commonly used.

3) Floating point numbers use a sign, significand, and exponent to represent real numbers in a normalized format like ±.significand × 2exponent.

Arithmetic for Computers

Arithmetic for ComputersMD. ABU TALHA This document discusses arithmetic operations for computers including addition, subtraction, and overflow. It provides examples of adding and subtracting numbers in binary format. It explains the basic rules for addition and subtraction of binary numbers. It also discusses overflow that can occur during arithmetic operations and how overflow is handled differently for signed versus unsigned integers in MIPS computers. Overflow is detected using exceptions in MIPS.

Arithmetic Logic Unit (ALU)

Arithmetic Logic Unit (ALU)Student An arithmetic logic unit (ALU) is a digital electronic circuit that performs arithmetic and bitwise logical operations on integer binary numbers.

This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units.

A single CPU, FPU or GPU may contain multiple ALUs

History Of ALU:Mathematician John von Neumann proposed the ALU concept in 1945 in a report on the foundations for a new computer called the EDVAC(Electronic Discrete Variable Automatic Computer

Typical Schematic Symbol of an ALU:A and B: the inputs to the ALU

R: Output or Result

F: Code or Instruction from the

Control Unit

D: Output status; it indicates cases

Circuit operation:An ALU is a combinational logic circuit

Its outputs will change asynchronously in response to input changes

The external circuitry connected to the ALU is responsible for ensuring the stability of ALU input signals throughout the operation

ALU arithmetic logic unit

ALU arithmetic logic unitKarthik Prof. The document discusses the arithmetic logic unit (ALU), which is a digital circuit that performs arithmetic and logical operations in a central processing unit (CPU). It first reviews basic CPU concepts like registers and the control unit. It then defines the ALU and describes its typical components and symbol. The remainder of the document demonstrates how to build a simple 1-bit ALU and discusses how multiple 1-bit ALUs can be combined into a larger 32-bit ALU. Useful online resources on ALUs and CPU architecture are also provided.

Arithmetic Process in Computer Systems

Arithmetic Process in Computer SystemsS N M P Simamora The document discusses arithmetic operations in digital computers. It describes how the arithmetic unit performs additions, subtractions, multiplications, and divisions by taking information from memory and processing it. It also explains how serial and parallel adders work to perform addition operations through shifting and adding bits. The document further discusses the complement technique for representing positive and negative numbers in binary, including using 1s and 0s to indicate sign and how to write numbers in signed and 2's complement form.

Arithmetic Logic Unit .

Arithmetic Logic Unit .Deyaa Ahmed In computing, an arithmetic logic unit (ALU) is a digital circuit that performs arithmetic and logical operations. The ALU is a fundamental building block of the central processing unit (CPU) of a computer, and even the simplest microprocessors contain one for purposes such as maintaining timers. The processors found inside modern CPUs and graphics processing units (GPUs) accommodate very powerful and very complex ALUs; a single component may contain a number of ALUs.

arithmetic logic unit

arithmetic logic unitShimak Sharook The document discusses the arithmetic logic unit (ALU), which performs arithmetic and logical operations in a computer. It describes how the ALU was proposed by John Von Neumann in 1945 and is a digital circuit that performs integer calculations and logical operations. The ALU is part of the computer's microprocessor and is used to perform arithmetic operations like addition and subtraction using binary code, as well as logical operations like AND and OR.

ALU

ALURamasubbu .P This document discusses the arithmetic logic unit (ALU) and its role in a central processing unit (CPU). It begins with an overview of the ALU and its functions, including that it performs arithmetic and logical operations. The document then shows a typical schematic symbol for an ALU and builds a sample 1-bit ALU circuit. It concludes by mentioning how ALUs can be expanded by connecting more 1-bit circuits in parallel.

Arithmetic logic units

Arithmetic logic unitsowaisahmad125 This document discusses binary addition, subtraction, half adders, full adders, 2's complement representation, and 2's complement adders that can perform both addition and subtraction of binary numbers. It explains how to perform binary addition and subtraction by hand, defines half adders and full adders as logic circuits, describes how 2's complement representation allows for signed binary numbers, and shows how a 2's complement adder works by selectively inverting one of the input numbers to perform either addition or subtraction.

Computer Architecture – An Introduction

Computer Architecture – An IntroductionDilum Bandara Overview on high-level design of internal components of a computer. Cover step-by-step execution of a program through ALU while accessing & updating registers

Basic structure of computers

Basic structure of computersKumar The document summarizes the basic functional units and operations of a computer system. It describes how a computer contains a central processing unit (CPU) that includes an arithmetic logic unit (ALU) and control unit to execute instructions. A computer also has memory to store programs and data, and input/output (I/O) devices to accept and output information. The CPU fetches instructions from memory, retrieves operands from memory or registers, performs operations in the ALU, and stores results back to memory or registers. The control unit coordinates the flow of data and execution of instructions. Performance can be improved by increasing clock speed, reducing the number of steps per instruction through pipelining and superscalar techniques, and optimizing compilers

Love as it is to me

Love as it is to meprasadpawaskar This story is about Emma, an artist who sketches daily at a cafe, and Steve, a man who drives by each day. They see each other but don't speak until one day when Steve is unable to get change from a newspaper vendor. He sees Emma offering change inside the cafe. They finally speak, realizing their connection after seeing each other from afar. The story suggests they will live happily ever after.

who-are-you

who-are-youprasadpawaskar The document discusses either hiding in the shade of a tree from the sun's rays or going out to enjoy God's warmth. It states that one must have stood in God's light once to recognize the shadow as providing freshness, and to recognize how incredible God's world is. The document suggests inviting God into your life to more easily recognize that you are part of his incredible creation.

Midterm 1

Midterm 1IIUM The document outlines a midterm exam covering limits, continuity, derivatives, and finding asymptotes and tangent lines. It contains 5 questions: 1) evaluating limits, 2) determining continuity and differentiability, 3) finding asymptotes, 4) taking derivatives, and 5) finding the equation of a tangent line.

Microprocessor laboratory 03 Arithmetic Operation (Additional and Subtraction)

Microprocessor laboratory 03 Arithmetic Operation (Additional and Subtraction)Arkhom Jodtang This document is a laboratory report from Arkhom Jodtang of the Avionics Division of CATC Thailand. It describes Laboratory 3 on arithmetic operations using a Microprocessor (MCS-51) system that was conducted on March 22, 2016. The laboratory focused on performing and understanding basic arithmetic operations like addition, subtraction, multiplication and division using the microprocessor.

Microprocessor

MicroprocessorAdarsh Barnwal The document is a presentation on an introduction to microprocessors. It defines a microprocessor as an electronic circuit that functions as the central processing unit (CPU) of a computer. It then discusses the main components and architecture of a microprocessor, including the timing and control unit, arithmetic logic unit, interface section, and register section. It provides examples of the 8085 microprocessor pin diagram and block diagram to illustrate these sections.

Ad

Similar to Csc1401 lecture03 - computer arithmetic - arithmetic and logic unit (alu) (20)

Integer represention

Integer representionSaif Ullah This document discusses arithmetic and logic unit (ALU) operations in a computer system. It covers:

1) The ALU is the part of the computer that performs arithmetic and logical operations on data using basic digital logic gates. All other computer elements bring data to the ALU and return results.

2) Integer numbers can be represented in binary using sign-magnitude or twos-complement formats. Twos-complement is more commonly used as it allows for simpler addition and negation operations.

3) The document explains how integer addition, subtraction, multiplication and division are performed in binary using the various representation schemes through examples and flowcharts. Special cases and algorithms like Booth's method for multiplying negative numbers are also

index of all of the financial accounts in a company's general ledger. In shor...

index of all of the financial accounts in a company's general ledger. In shor...mayurjagdale4 index of all of the financial accounts in a company's general ledger. In short, it is an organizational tool that lists by category and line item all of the financial transactions that a company conducted during a specific accounting period

Computer Architecture refers to those attributes of a system that have a dire...

Computer Architecture refers to those attributes of a system that have a dire...mayurjagdale4 Computer Architecture refers to those attributes of a system that have a direct impact on

the logical execution of a program. Examples:

o the instruction set

o the number of bits used to represent various data types

o I/O mechanisms

o memory addressing techniques

CS304PC:Computer Organization and Architecture session 22 floating point arit...

CS304PC:Computer Organization and Architecture session 22 floating point arit...Guru Nanak Technical Institutions This document summarizes a session on floating point arithmetic operations. It discusses how floating point numbers are represented using the IEEE standard format, with a sign bit, exponent bits, and mantissa bits. It describes the basic operations of addition, subtraction, multiplication, and division of floating point numbers. These operations involve aligning the mantissa, adding or subtracting exponents, and normalizing the result. The document also discusses normalized representation, underflow, overflow, and biased exponents in floating point number representation and arithmetic.

CS304PC:Computer Organization and Architecture Session 19 Addition and subtra...

CS304PC:Computer Organization and Architecture Session 19 Addition and subtra...Guru Nanak Technical Institutions This document provides an overview of the CS304PC course on Computer Organization and Architecture. It lists the textbook and references for the course. The topics to be covered in Session 19 include addition and subtraction algorithms, multiplication algorithms, division algorithms, and floating-point and decimal arithmetic operations. The session will discuss how these arithmetic operations are implemented in hardware using registers, adders, comparators, and other components.

Computer Oraganizaation.pptx

Computer Oraganizaation.pptxbmangesh The document provides an introduction to computer organization and digital logic concepts. It discusses number systems such as binary, decimal, octal and hexadecimal used in computing. It also covers topics like binary addition and subtraction, decimal representation in computers using fixed-point and floating-point notations, excess-3 code, Gray code and various alphanumeric codes. Finally, it introduces common logic gates such as AND, OR and NOT that serve as building blocks of digital circuits.

CS304PC:Computer Organization and Architecture Session 17 Complements and fix...

CS304PC:Computer Organization and Architecture Session 17 Complements and fix...Guru Nanak Technical Institutions CS304PC:Computer Organization and Architecture Session 17 Complements and fixed points representations

Floating point arithmetic operations (1)

Floating point arithmetic operations (1)cs19club This document discusses floating point arithmetic operations including:

- The components of a floating point number including the mantissa and exponent.

- Normalization of floating point numbers to have a leading nonzero digit in the mantissa.

- Common floating point operations like addition, subtraction, multiplication, and division and how they are performed.

- The IEEE 754 standard for representing floating point numbers.

- How floating point arithmetic is implemented in hardware including registers and adders used to process mantissas and exponents.

Unit 2 Arithmetic

Unit 2 ArithmeticBalaji Vignesh Digital computers represent all data, including numbers, using the binary number system. There are two main methods for representing real numbers: fixed-point notation reserves a fixed number of bits for the integer and fractional parts, while floating-point notation reserves bits for the significand and exponent to allow more flexibility in the number of fractional digits. Fixed-point has better performance but a more limited range, while floating-point can represent a wider range of values but requires more complex operations. Common number representations like two's complement are used to support arithmetic operations.

Unit_3 OF COMPUTER ARCHITECTUREUnit.pptx

Unit_3 OF COMPUTER ARCHITECTUREUnit.pptxShwetamaurya36 Unit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHITECTUREUnit_3 OF COMPUTER ARCHI

Digital fundamendals r001a

Digital fundamendals r001aarunachalamr16 Digital Arithmetic: Operations and Circuits discusses binary addition, subtraction, multiplication, and division. It also covers different systems for representing signed numbers, including sign-magnitude, 1's complement, and 2's complement. Key topics include performing arithmetic using the 2's complement system, detecting overflow, and representing decimal values in binary coded decimal. The document provides examples and review questions to illustrate binary arithmetic concepts.

Number Systems.ppt

Number Systems.pptzorogoh2 The binary number system and digital codes are fundamental to computers and to digital electronics in general. You will learn Binary addition, subtraction, multiplication, and Division.

Arithmetic circuits

Arithmetic circuitsSanjay Saluth This document discusses digital arithmetic circuits. It defines competencies around binary addition, 1's and 2's complement representations, and arithmetic operations. Key concepts covered include half adders, full adders, parallel addition, and 8-bit addition. Worked examples demonstrate converting between decimal and binary representations, performing addition and subtraction using 2's complement, and designing multi-bit adders.

Unit I-L1 - Basics of Digital Computer Organization and Architecture

Unit I-L1 - Basics of Digital Computer Organization and Architectureamanseerat89 Unit I-L1 - Basics of Digital Computer Organization and Architecture

Unit 1 - Introduction to Digital Computer (computer organization.pdf

Unit 1 - Introduction to Digital Computer (computer organization.pdfchibunnajoe31 This material introduces the concept of internet and computer system

2s complement arithmetic

2s complement arithmeticSanjay Saluth This document discusses 2's complement arithmetic in digital electronics. It explains that subtracting one number from another is the same as making one number negative and adding them. It then demonstrates how to represent negative numbers in binary by taking the 2's complement of a number, which involves complementing all its digits and adding 1. Various examples are provided of adding positive and negative binary numbers by taking the 2's complement of negative terms before adding. The most significant bit is identified as the sign bit that determines if a number is positive or negative.

2sComplementArithmetic1.ppt

2sComplementArithmetic1.pptSathishkumar.V This document discusses 2's complement arithmetic in digital electronics. It explains that subtracting one number from another is the same as making one number negative and adding. It then demonstrates how to represent negative numbers in binary by taking the 2's complement of positive numbers. Finally, it provides examples of adding positive and negative binary numbers using the 2's complement process.

2sComplementArithmetic1.ppt

2sComplementArithmetic1.pptMeghadriGhosh4 This document discusses 2's complement arithmetic in digital electronics. It explains that subtracting one number from another is the same as making one number negative and adding. It then demonstrates how to represent negative numbers in binary by taking the 2's complement of positive numbers. Finally, it provides examples of adding positive and negative binary numbers using the 2's complement process.

2sComplementArithmetic1 lecture slides ppt

2sComplementArithmetic1 lecture slides pptnashitahalwaz95 This document discusses 2's complement arithmetic in digital electronics. It explains that subtracting one number from another is the same as making one number negative and adding. It then demonstrates how to represent negative numbers in binary by taking the 2's complement of positive numbers. Finally, it provides examples of adding positive and negative binary numbers using the 2's complement process.

CS304PC:Computer Organization and Architecture session 22 floating point arit...

CS304PC:Computer Organization and Architecture session 22 floating point arit...Guru Nanak Technical Institutions

CS304PC:Computer Organization and Architecture Session 19 Addition and subtra...

CS304PC:Computer Organization and Architecture Session 19 Addition and subtra...Guru Nanak Technical Institutions

CS304PC:Computer Organization and Architecture Session 17 Complements and fix...

CS304PC:Computer Organization and Architecture Session 17 Complements and fix...Guru Nanak Technical Institutions

Ad

More from IIUM (20)

How to use_000webhost

How to use_000webhostIIUM 1. Create an account on 000webhost.com and choose a free subdomain as the domain name for your project website.

2. After registering, open the activation email and sign in to the 000webhost control panel using your credentials.

3. Use an FTP client like FileZilla to connect to the 000webhost server using the FTP details, and upload all project files to the public_html folder.

Chapter 2

Chapter 2IIUM This document discusses text elements in multimedia presentations. It covers topics like the importance of text, understanding fonts and typefaces, using text elements like menus and buttons, and hypertext. Computers and text are also examined, including font types like PostScript, TrueType, and OpenType as well as character sets. Multimedia and hypertext systems are defined, along with how users can navigate and search through linked nodes and anchors.

Chapter 1

Chapter 1IIUM This document discusses multimedia and its applications. It defines multimedia as a combination of different media types, and notes that multimedia becomes interactive when users can control elements. It then describes common applications of multimedia in business, education, homes, and public spaces. Finally, it discusses methods of delivering multimedia, including via CD-ROM, DVD, and virtual reality.

Kreydle internship-multimedia

Kreydle internship-multimediaIIUM The Kreydle Internship Program provides a 5-week training program for interns to learn multimedia skills like video production, photography, and presentation design. Interns are mentored and work on projects aligned with quarterly objectives and key results. The program teaches skills in areas like storyboarding, recording, editing, and teaches interns to create an engaging LinkedIn profile and internship experience video. Interns learn our company culture of learning, sharing, and accountability.

03phpbldgblock

03phpbldgblockIIUM PHP scripts contain PHP code interspersed with HTML. PHP code is contained within opening <?php and closing ?> tags and is interpreted by the Zend engine before the page is sent to the browser. There are different styles of PHP tags like XML, short open, script, and ASP styles. PHP supports core data types like integers, floats, strings, booleans and other special types. Variables in PHP begin with a $ sign and have a name, value, and type. Constants are values that cannot change during script execution and are defined using the define() function.

Chap2 practice key

Chap2 practice keyIIUM The document provides requirements for creating an entity relationship diagram (ERD) for a National Hockey League database. It specifies that the ERD should include entities for teams, players, games and their attributes and relationships. A sample ERD is provided that models teams as having a name, city, coach and captain, players as belonging to teams and having attributes, and games as connecting two teams with a date and score.

Group p1

Group p1IIUM This document provides instructions for a group assignment on data structures and algorithms. It contains 4 questions:

1. Determine the output of sample C++ code that performs a binary search on an array to find a given input value.

2. Represent -8, 8, and 0.3125 in their corresponding 4-bit signed integer and 16-bit floating point binary formats or explain why it is not possible.

3. Circle properties that describe arrays as a data structure and explain the selection. The properties are basic/compound, static/dynamic, and linear/non-linear.

4. For a 3D array stored in column-wise format: a) calculate the address of a given element, and b

Tutorial import n auto pilot blogspot friendly seo

Tutorial import n auto pilot blogspot friendly seoIIUM Teks ini memberikan tutorial cara mengimpor konten blog dan mengotomatisasi pembaharuan blog di Blogspot tanpa perangkat lunak, dengan memanfaatkan fitur impor RSS dan otomatisasi IFTTT. Beberapa langkah kuncinya adalah menemukan blog target melalui pencarian Google, mengambil RSS feed-nya, mengimpor konten ke blog sendiri di Blogspot, lalu mengatur IFTTT untuk secara otomatis mengambil setiap update dari blog target. Penulis menegaskan

Visual sceneperception encycloperception-sage-oliva2009

Visual sceneperception encycloperception-sage-oliva2009IIUM Visual scenes are composed of objects and surfaces arranged in a meaningful spatial layout. Perceiving scenes involves understanding the overall meaning or "gist" of the scene from a single glance, even though details may not be perceived or remembered. Scene perception relies heavily on global spatial layout and statistical regularities rather than individual object recognition. The brain reconstructs scenes using memory, knowledge and expectations which can lead to errors like boundary extension or change blindness where details are missed or falsely remembered.

03 the htm_lforms

03 the htm_lformsIIUM This document discusses HTML forms and how they interact with PHP. It begins by explaining that forms are used to collect and process user input data on websites. It then covers key topics like the structure and elements of an HTML form, how forms send data to a server via GET and POST methods, and how PHP can then access and use the submitted form data on the server-side. Examples are provided throughout to illustrate form markup, form submission handling in PHP, and how data is transmitted between the client and server.

Exercise on algo analysis answer

Exercise on algo analysis answerIIUM This document appears to be notes from a data structures and algorithms course, listing time complexities of various algorithms. It includes big O notations for operations that take constant, linear, quadratic, and cubic time, as well as square root and log time. Code examples are used only to explain algorithms at a high level without specific programming syntax.

Redo midterm

Redo midtermIIUM This document contains multiple choice and short answer questions about data structures such as arrays, linked lists, stacks, queues, and trees. The multiple choice questions test knowledge of the basic properties and applications of these data structures. The short answer questions involve coding examples using recursion, stacks, queues, and linked lists to solve problems.

Heaps

HeapsIIUM The document discusses priority queues and binary heaps. It explains that priority queues store tasks based on priority level and ensure the highest priority task is at the head of the queue. Binary heaps are the underlying data structure used to implement priority queues. The key operations on a binary heap are insert and deleteMin. Insert involves adding an element and percolating it up the heap, while deleteMin removes the minimum element and percolates the replacement down. Both operations have O(log n) time complexity. The document provides examples and pseudocode for building a heap from a list of elements in O(n) time using a buildHeap method.

Report format

Report formatIIUM This document provides guidelines for preparing final year project reports at the Kulliyyah of Engineering at the International Islamic University Malaysia. It outlines requirements for report formatting, including paper size and type, font styles and sizes, margins, page numbering, headings, paragraphs, and binding. It also describes the required contents and order, including a cover page, title page, abstract, acknowledgements, table of contents, body of the text organized into chapters, and references. The body of the text must include chapters on introduction, theoretical background or literature review, methodology, presentation of results, discussion, and conclusions.

Edpuzzle guidelines

Edpuzzle guidelinesIIUM To use Edpuzzle, students should go to edpuzzle.com, log in or create an account using their Google account or by creating a new account, and update their profile name to their matrix number. Students then join their class by entering the given class code provided by their teacher.

Group assignment 1 s21516

Group assignment 1 s21516IIUM This document outlines requirements for a group assignment to create a simple website using HTML. Students must create a web hosting account and develop a main page with two sections - a 20% wide left menu and 80% wide right display area. The menu should include hyperlinks to individual member pages on the right. Each member page should include that person's photo, name, student ID, and email in an HTML table. Students should save all files in a compressed folder named after their group, submit via the learning platform, and publish the complete site online. The assignment has guidelines around group size, submissions, and maintaining the published site.

Avl tree-rotations

Avl tree-rotationsIIUM This document provides an overview of AVL tree rotations, including left, right, left-right and right-left rotations. It explains how each rotation works by restructuring the nodes and subtrees. Situations requiring each type of rotation are demonstrated through examples. Rules for determining which rotation to use based on whether the tree is left or right heavy and the balance of related subtrees are also outlined. The document aims to explain rotations, when they are needed to rebalance the tree, and how to identify the appropriate rotation to apply in different unbalanced scenarios.

Week12 graph

Week12 graph IIUM The document discusses graphs and graph algorithms. It defines graph terminology like vertices, edges, adjacency matrix, and adjacency list representations of graphs. It then explains the breadth-first search (BFS) algorithm through an example, showing how BFS visits vertices level-by-level starting from the source vertex. BFS uses a queue and predecessor array to keep track of the shortest paths found. The document also briefly introduces depth-first search (DFS) and shows the beginning of an example DFS.

Recently uploaded (20)

Dastur_ul_Amal under Jahangir Key Features.pptx

Dastur_ul_Amal under Jahangir Key Features.pptxomorfaruqkazi Dastur_ul_Amal under Jahangir Key Features

The Dastur-ul-Amal (or Dasturu’l Amal) of Emperor Jahangir is a key administrative document from the Mughal period, particularly relevant during Jahangir’s reign (1605–1627). The term "Dastur-ul-Amal" broadly translates to "manual of procedures" or "regulations for administration", and in Jahangir’s context, it refers to his set of governance principles, administrative norms, and regulations for court officials and provincial administration.

Antepartum fetal surveillance---Dr. H.K.Cheema pdf.pdf

Antepartum fetal surveillance---Dr. H.K.Cheema pdf.pdfDr H.K. Cheema Ante natal fetal surveillance is the need of the hour to decrease fetal morbidity & mortality, Medical students need to be aware of it.

IPL QUIZ | THE QUIZ CLUB OF PSGCAS | 2025.pdf

IPL QUIZ | THE QUIZ CLUB OF PSGCAS | 2025.pdfQuiz Club of PSG College of Arts & Science GUESS WHO'S HERE TO ENTERTAIN YOU DURING THE INNINGS BREAK OF IPL.

THE QUIZ CLUB OF PSGCAS BRINGS YOU A QUESTION SUPER OVER TO TRIUMPH OVER IPL TRIVIA.

GET BOWLED OR HIT YOUR MAXIMUM!

How to Manage Amounts in Local Currency in Odoo 18 Purchase

How to Manage Amounts in Local Currency in Odoo 18 PurchaseCeline George In this slide, we’ll discuss on how to manage amounts in local currency in Odoo 18 Purchase. Odoo 18 allows us to manage purchase orders and invoices in our local currency.

Unit 5 ACUTE, SUBACUTE,CHRONIC TOXICITY.pptx

Unit 5 ACUTE, SUBACUTE,CHRONIC TOXICITY.pptxMayuri Chavan Unit 5 ACUTE, SUBACUTE,CHRONIC TOXICITY.pptx

Cyber security COPA ITI MCQ Top Questions

Cyber security COPA ITI MCQ Top QuestionsSONU HEETSON Cyber security COPA ITI MCQ questions and answers important for theory Exam paper NCVT/SCVT

Conditions for Boltzmann Law – Biophysics Lecture Slide

Conditions for Boltzmann Law – Biophysics Lecture SlidePKLI-Institute of Nursing and Allied Health Sciences Lahore , Pakistan. This presentation covers the conditions required for the application of Boltzmann Law, aimed at undergraduate nursing and allied health science students studying Biophysics. It explains the prerequisites for the validity of the law, including assumptions related to thermodynamic equilibrium, distinguishability of particles, and energy state distribution.

Ideal for students learning about molecular motion, statistical mechanics, and energy distribution in biological systems.

"Bridging Cultures Through Holiday Cards: 39 Students Celebrate Global Tradit...

"Bridging Cultures Through Holiday Cards: 39 Students Celebrate Global Tradit...AlionaBujoreanu Holiday Exchanging Cards iEARN Project.

"Mihai Eminescu"PI TL Cahul Moldova.

MICROBIAL GENETICS -tranformation and tranduction.pdf

MICROBIAL GENETICS -tranformation and tranduction.pdfDHARMENDRA SAHU MICROBIAL GENETICS -Transformation and Tranduction.pdf for Medical student

U3 ANTITUBERCULAR DRUGS Pharmacology 3.pptx

U3 ANTITUBERCULAR DRUGS Pharmacology 3.pptxMayuri Chavan U3 ANTITUBERCULAR DRUGS Pharmacology 3.pptx

How to Change Sequence Number in Odoo 18 Sale Order

How to Change Sequence Number in Odoo 18 Sale OrderCeline George In this slide, we’ll discuss on how to change sequence number in Odoo 18 Sale Order. In Odoo, sequences are used to generate unique identifiers for records. These identifiers are often displayed as reference numbers, such as invoice numbers, purchase order numbers, or customer numbers.

The role of wall art in interior designing

The role of wall art in interior designingmeghaark2110 Wall art and wall patterns are not merely decorative elements, but powerful tools in shaping the identity, mood, and functionality of interior spaces. They serve as visual expressions of personality, culture, and creativity, transforming blank and lifeless walls into vibrant storytelling surfaces. Wall art, whether abstract, realistic, or symbolic, adds emotional depth and aesthetic richness to a room, while wall patterns contribute to structure, rhythm, and continuity in design. Together, they enhance the visual experience, making spaces feel more complete, welcoming, and engaging. In modern interior design, the thoughtful integration of wall art and patterns plays a crucial role in creating environments that are not only beautiful but also meaningful and memorable. As lifestyles evolve, so too does the art of wall decor—encouraging innovation, sustainability, and personalized expression within our living and working spaces.

BÀI TẬP BỔ TRỢ TIẾNG ANH 9 THEO ĐƠN VỊ BÀI HỌC - GLOBAL SUCCESS - CẢ NĂM (TỪ...

BÀI TẬP BỔ TRỢ TIẾNG ANH 9 THEO ĐƠN VỊ BÀI HỌC - GLOBAL SUCCESS - CẢ NĂM (TỪ...Nguyen Thanh Tu Collection https://app.box.com/s/yfwqwcillls0z4p34958pr8nj0b4udyr

2025 The Senior Landscape and SET plan preparations.pptx

2025 The Senior Landscape and SET plan preparations.pptxmansk2 2025 The Senior Landscape and SET plan preparations.pptx

UPSA JUDGEMENT.pdfCopyright Infringement: High Court Rules against UPSA: A Wa...

UPSA JUDGEMENT.pdfCopyright Infringement: High Court Rules against UPSA: A Wa...businessweekghana Copyright Infringement: High Court Rules against UPSA: A Wake-Up Call for Educational Institutions

YSPH VMOC Special Report - Measles Outbreak Southwest US 5-17-2025 .pptx

YSPH VMOC Special Report - Measles Outbreak Southwest US 5-17-2025 .pptxYale School of Public Health - The Virtual Medical Operations Center (VMOC) As of 5/17/25, the Southwestern outbreak has 865 cases, including confirmed and pending cases across Texas, New Mexico, Oklahoma, and Kansas. Experts warn this is likely a severe undercount. The situation remains fluid, though we are starting to see a significant reduction in new cases in Texas. Experts project the outbreak could last up to a year.

CURRENT CASE COUNT: 865 (As of 5/17/2025)

- Texas: 720 (+2) (62% of cases are in Gaines County)

- New Mexico: 74 (+3) (92.4% of cases are from Lea County)

- Oklahoma: 17

- Kansas: 54 (38.89% of the cases are from Gray County)

HOSPITALIZATIONS: 102

- Texas: 93 - This accounts for 13% of all cases in Texas.

- New Mexico: 7 – This accounts for 9.47% of all cases in New Mexico.

- Kansas: 2 - This accounts for 3.7% of all cases in Kansas.

DEATHS: 3

- Texas: 2 – This is 0.28% of all cases

- New Mexico: 1 – This is 1.35% of all cases

US NATIONAL CASE COUNT: 1,038 (Confirmed and suspected)

INTERNATIONAL SPREAD (As of 5/17/2025)

Mexico: 1,412 (+192)

- Chihuahua, Mexico: 1,363 (+171) cases, 1 fatality, 3 hospitalizations

Canada: 2,191 (+231) (Includes

Ontario’s outbreak, which began in November 2024)

- Ontario, Canada – 1,622 (+182), 101 (+18) hospitalizations

Conditions for Boltzmann Law – Biophysics Lecture Slide

Conditions for Boltzmann Law – Biophysics Lecture SlidePKLI-Institute of Nursing and Allied Health Sciences Lahore , Pakistan.

BÀI TẬP BỔ TRỢ TIẾNG ANH 9 THEO ĐƠN VỊ BÀI HỌC - GLOBAL SUCCESS - CẢ NĂM (TỪ...

BÀI TẬP BỔ TRỢ TIẾNG ANH 9 THEO ĐƠN VỊ BÀI HỌC - GLOBAL SUCCESS - CẢ NĂM (TỪ...Nguyen Thanh Tu Collection

YSPH VMOC Special Report - Measles Outbreak Southwest US 5-17-2025 .pptx

YSPH VMOC Special Report - Measles Outbreak Southwest US 5-17-2025 .pptxYale School of Public Health - The Virtual Medical Operations Center (VMOC)

Csc1401 lecture03 - computer arithmetic - arithmetic and logic unit (alu)

- 1. Madam Raini Hassan Office: C5 - 23, Level 5, KICT Building Department: Computer Science Emails: [email protected], [email protected] 1Semester II 2014/2015

- 2. Du’a for Study Semester II 2014/2015 2

- 3. LECTURE 03 Computer Arithmetic: Arithmetic and Logic Unit (ALU) (Chapter 10)

- 4. Arithmetic & Logic Unit (ALU) • Part of the computer that actually performs arithmetic and logical operations on data • All of the other elements of the computer system are there mainly to bring data into the ALU for it to process and then to take the results back out • Based on the use of simple digital logic devices that can store binary digits and perform simple Boolean logic operations

- 5. ALU Inputs and Outputs

- 6. Integer Representations • In the binary number system arbitrary numbers can be represented with: – The digits zero and one – The minus sign (for negative numbers) – The period, or radix point (for numbers with a fractional component) – For purposes of computer storage and processing we do not have the benefit of special symbols for the minus sign and radix point – Only binary digits (0,1) may be used to represent numbers

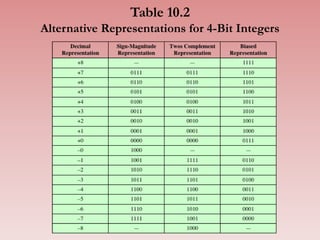

- 7. Integer Representations • There are 4 commonly known (1 not common) integer representations. • All have been used at various times for various reasons. 1. Unsigned 2. Sign Magnitude 3. One’s Complement 4. Two’s Complement 5. Biased (not commonly known)

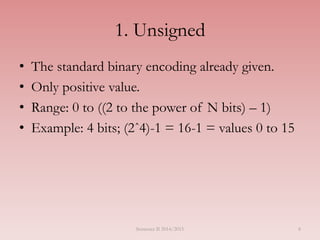

- 8. 1. Unsigned • The standard binary encoding already given. • Only positive value. • Range: 0 to ((2 to the power of N bits) – 1) • Example: 4 bits; (2ˆ4)-1 = 16-1 = values 0 to 15 Semester II 2014/2015 8

- 9. 1. Unsigned (Cont’d.) Semester II 2014/2015 9

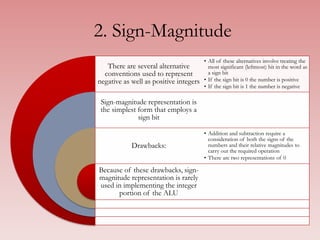

- 10. 2. Sign-Magnitude There are several alternative conventions used to represent negative as well as positive integers Sign-magnitude representation is the simplest form that employs a sign bit Drawbacks: Because of these drawbacks, sign- magnitude representation is rarely used in implementing the integer portion of the ALU • All of these alternatives involve treating the most significant (leftmost) bit in the word as a sign bit • If the sign bit is 0 the number is positive • If the sign bit is 1 the number is negative • Addition and subtraction require a consideration of both the signs of the numbers and their relative magnitudes to carry out the required operation • There are two representations of 0

- 11. 2. Sign-Magnitude (Cont’d.) • It is a human readable way of getting both positive and negative integers. • The hardware that does arithmetic on sign magnitude integers. • Not fast. 2-11

- 12. 2. Sign-Magnitude (Cont’d.) • Left most bit is sign bit • 0 means positive • 1 means negative • +18 = 00010010 • -18 = 10010010 2-12

- 13. 3. One’s Complement • Used to get two’s complement integers. • Nowadays, it is not being applied to any of the machines. • Stated in this slide for historical purpose. Semester II 2014/2015 13

- 14. 4. Two’s Complement • Uses the most significant bit as a sign bit • Differs from sign-magnitude representation in the way that the other bits are interpreted Table 10.1 Characteristics of Twos Complement Representation and Arithmetic

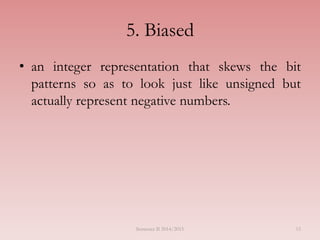

- 15. 5. Biased • an integer representation that skews the bit patterns so as to look just like unsigned but actually represent negative numbers. Semester II 2014/2015 15

- 16. Table 10.2 Alternative Representations for 4-Bit Integers

- 17. Range Extension – Range of numbers that can be expressed is extended by increasing the bit length – In sign-magnitude notation this is accomplished by moving the sign bit to the new leftmost position and fill in with zeros – This procedure will not work for twos complement negative integers – Rule is to move the sign bit to the new leftmost position and fill in with copies of the sign bit – For positive numbers, fill in with zeros, and for negative numbers, fill in with ones – This is called sign extension

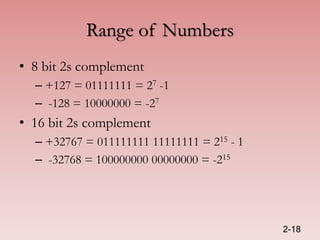

- 18. Range of Numbers • 8 bit 2s complement – +127 = 01111111 = 27 -1 – -128 = 10000000 = -27 • 16 bit 2s complement – +32767 = 011111111 11111111 = 215 - 1 – -32768 = 100000000 00000000 = -215 2-18

- 19. Negation • Twos complement operation – Take the Boolean complement of each bit of the integer (including the sign bit) – Treating the result as an unsigned binary integer, add 1 – The negative of the negative of that number is itself: +18 = 00010010 (twos complement) bitwise complement = 11101101 + 1 11101110 = -18 -18 = 11101110 (twos complement) bitwise complement = 00010001 + 1 00010010 = +18

- 20. Negation Special Case 1 0 = 00000000 (twos complement) Bitwise complement = 11111111 Add 1 to LSB + 1 Result 100000000 Overflow is ignored, so: - 0 = 0

- 21. Negation Special Case 2 -128 = 10000000 (twos complement) Bitwise complement = 01111111 Add 1 to LSB + 1 Result 10000000 So: -(-128) = -128 X Monitor MSB (sign bit) It should change during negation

- 22. OVERFLOW RULE: If two numbers are added, and they are both positive or both negative, then overflow occurs if and only if the result has the opposite sign.

- 23. Addition

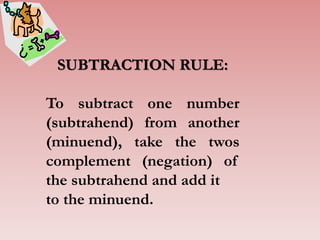

- 24. SUBTRACTION RULE: To subtract one number (subtrahend) from another (minuend), take the twos complement (negation) of the subtrahend and add it to the minuend.

- 25. Subtraction

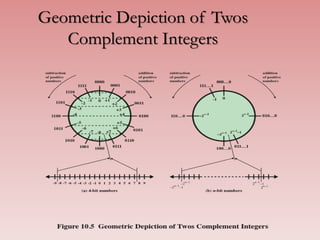

- 26. Geometric Depiction of Twos Complement Integers

- 27. Hardware for Addition and Subtraction

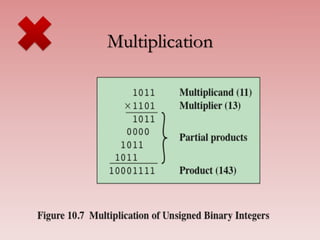

- 28. Multiplication

- 32. Comparison

- 34. Division

- 36. Example of Restoring Twos Complement Division

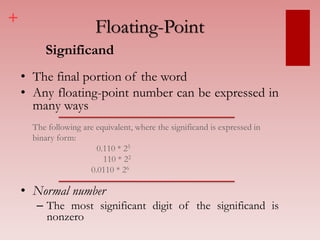

- 37. + Floating-Point Representation • With a fixed-point notation it is possible to represent a range of positive and negative integers centered on or near 0 • By assuming a fixed binary or radix point, this format allows the representation of numbers with a fractional component as well • Limitations: – Very large numbers cannot be represented nor can very small fractions – The fractional part of the quotient in a division of two large numbers could be lost Principles

- 38. Typical 32-Bit Floating-Point Format

- 39. + Floating-Point • The final portion of the word • Any floating-point number can be expressed in many ways • Normal number – The most significant digit of the significand is nonzero Significand The following are equivalent, where the significand is expressed in binary form: 0.110 * 25 110 * 22 0.0110 * 26

- 40. IEEE Standard 754 Most important floating-point representation is defined Standard was developed to facilitate the portability of programs from one processor to another and to encourage the development of sophisticated, numerically oriented programs Standard has been widely adopted and is used on virtually all contemporary processors and arithmetic coprocessors IEEE 754-2008 covers both binary and decimal floating- point representations

- 41. IEEE 754 Formats

- 42. Floating-Point Addition and Subtraction