Implementation of 1 bit full adder using gate diffusion input (gdi) technique

Download as pptx, pdf14 likes7,533 views

This document discusses the implementation of a 1-bit full adder circuit using the Gate Diffusion Input (GDI) technique. GDI is introduced as a low-power logic design style that can reduce transistor counts, power consumption, and propagation delay compared to traditional CMOS designs. The document first reviews the advantages of GDI and the basic GDI cell functions. It then describes how a conventional CMOS 1-bit full adder works before presenting the design of a XOR-based and GDI-based 1-bit full adder. Transient analysis and comparisons show that the GDI full adder uses fewer transistors and has lower power and delay than traditional CMOS designs. The document concludes that GDI is an

1 of 27

Downloaded 375 times

Ad

Recommended

Design Hierarchy, Concepts of Regularity, Modularity and Locality

Design Hierarchy, Concepts of Regularity, Modularity and LocalityAdiSeshu16 This document discusses concepts for managing design complexity, including design hierarchy, regularity, modularity, and locality. It provides examples of how hierarchical decomposition can divide a complex system into sub-modules, with each level becoming more manageable. Regularity means using similar blocks as much as possible. Modularity defines well-defined functions and interfaces between blocks to allow independent and parallel design. Locality keeps connections local to avoid long interconnect delays.

FPGA

FPGAsubin mathew FPGA are a special form of Programmable logic devices(PLDs) with higher densities as compared to custom ICs and capable of implementing functionality in a short period of time using computer aided design (CAD) software....by [email protected]

Introduction to VLSI Design

Introduction to VLSI DesignKalyan Acharjya Introduction of VLSI Design, Chip Development, Moore's Law. Its gives you the basic development overview of VLSI Technology

SHORT CHANNEL EFFECTS IN MOSFETS- VLSI DESIGN

SHORT CHANNEL EFFECTS IN MOSFETS- VLSI DESIGNNITHIN KALLE PALLY SHORT-CHANNEL EFFECTS

A MOSFET is considered to be short when the channel length ‘L’ is the same order of magnitude as the depletion-layer widths (xdD, xdS). The potential distribution in the channel now depends upon both, transverse field Ex, due to gate bias and also on the longitudinal field Ey, due to drain bias When the Gate channel length <<1 m, short channel effect becomes important .

This leads to many

undesirable effects in MOSFET.

The short-channel effects are attributed to two physical phenomena:

A) The limitation imposed on electron drift characteristics in the channel,

B) The modification of the threshold voltage due to the shortening channel length.

In particular five different short-channel effects can be distinguished:

1. Drain-induced barrier lowering and “Punch through”

2. Surface scattering

3. Velocity saturation

4. Impact ionization

5. Hot electrons

Vlsi physical design

Vlsi physical designI World Tech The document discusses the physical design process for VLSI circuits. It describes the main steps as partitioning, floor planning and placement, routing, layout optimization, and extraction and verification. The goals of physical design are to minimize signal delays, interconnection area, and power usage. Physical design transforms the logical structure of a circuit into its physical layout.

DOMINO LOGIC CIRCUIT (VLSI)

DOMINO LOGIC CIRCUIT (VLSI)AmiBokasoda Problems of dynamic logic circuits and how it is solved by Domino logic circuits, is explained over here. Why it is called domino and how domino logic works, that also explained here.

CMOS

CMOS AWANISHKUMAR84 The document discusses CMOS technology which uses both NMOS and PMOS transistors in a complementary way. It has low power dissipation as power is only consumed during switching. CMOS circuits like inverters, NAND and NOR gates are constructed using a pull-up network of PMOS transistors and a pull-down network of NMOS transistors. The fabrication of CMOS transistors involves depositing and patterning materials on a silicon wafer through lithography. CMOS has advantages like low power, high noise immunity and is widely used in applications like computers, processors and memory chips.

Verilog full adder in dataflow & gate level modelling style.

Verilog full adder in dataflow & gate level modelling style.Omkar Rane This document describes two different models for a full adder circuit - a dataflow model and a gate level model. The dataflow model uses assign statements to directly define the sum (s) and carry out (cout) outputs in terms of the inputs (a, b, cin). The gate level model builds the full adder using lower level logic gates like xor, and, or connected via internal wires to compute the sum and carry outputs.

Switch level modeling

Switch level modelingDevi Pradeep Podugu This document discusses switch level modeling in Verilog. It describes different types of transistor switches that can be used as primitives in Verilog, including nmos, pmos, rnmos, rpmos, and cmos switches. It also covers bidirectional switches like tran, tranif1, and examples of how to use the switches to model basic logic gates and memory cells like a RAM cell. Time delays can be specified for switches. Switch level modeling allows designing circuits using transistors directly in Verilog.

TMS320C5x

TMS320C5xDeekshithaReddy23 The TMS320C5x DSP architecture is based on the C25 with some enhancements. It uses a Harvard architecture with separate program and data memory buses. The CPU contains a CALU for arithmetic, PLU for logic, and ARAU for address calculations. On-chip memory includes ROM, DARAM, and SARAM. Peripherals include serial ports, timers, interrupts, and I/O. The architecture provides high performance with low power consumption and compatibility with prior C series DSPs.

VLSI subsystem design processes and illustration

VLSI subsystem design processes and illustrationVishal kakade This document discusses the design processes for digital subsystem design. It begins by outlining the objectives of design consideration, problem and solution, basic digital processor structure, and datapath. It then discusses general considerations for subsystem design such as lower unit cost and higher reliability. It presents some common problems in design like how to design complex systems efficiently. It proposes solutions like top-down design and partitioning the system. The document then illustrates the design processes through examples like designing a 4-bit shifter and ALU subsystem. It provides block diagrams, logic diagrams and layouts at different stages of the design process.

Introduction to Embedded Systems I: Chapter 2 (1st portion)

Introduction to Embedded Systems I: Chapter 2 (1st portion)Moe Moe Myint The document provides an introduction to embedded systems and covers several topics:

- The core components of embedded systems including microprocessors, microcontrollers, digital signal processors, programmable logic devices, and commercial off-the-shelf components.

- Memory technologies used in embedded systems such as ROM, RAM, and flash memory.

- Sensors, actuators, and interfacing components like LEDs, displays, and motors.

- Communication interfaces including I2C, SPI, UART, and wireless standards.

- Other system components like reset circuits, oscillators, and watchdog timers.

- PCBs and their role in embedded design.

The document aims to provide learning objectives on the building

CMOS fabrication n well process

CMOS fabrication n well processSouvikDatta22 CMOS fabrication using n-well process: This is an industrial process used for making a CMOS inverter circuit.

ASIC

ASICGourab Palui This document provides an overview of application specific integrated circuits (ASICs). It discusses the main types of ASICs including full custom, semi-custom (standard cell-based and gate array-based), and programmable. For semi-custom, it describes standard cell-based ASICs using predesigned logic cells and different types of gate arrays including channeled, channelless, and structured. The document also covers the design flow, economics, merits like improved speed and power consumption, and demirts such as high costs for redesigns.

Logic Synthesis

Logic SynthesisVandanaPagar1 Logic synthesis is the process of converting a high-level design description into an optimized gate-level representation using a standard cell library and design constraints. The process involves translating the RTL description into an unoptimized internal representation, optimizing the logic, technology mapping, and producing an optimized gate-level netlist. An example logic synthesis flow is described for a 4-bit magnitude comparator design from RTL to optimized gates.

ARM7-ARCHITECTURE

ARM7-ARCHITECTURE Dr.YNM This class notes is meant for Electronics students of SKU and RU and also for ECE students of other universities.

Asic design flow

Asic design flowyogeshwaran k The document describes the ASIC design flow, which consists of two main phases: logical design (frontend) and physical design (backend).

The logical design phase includes design entry, logic synthesis, system partitioning, and pre-layout simulation. This phase converts the design from HDL or schematic to a netlist.

The physical design phase includes floorplanning, placement, routing, circuit extraction, and post-layout simulation. This phase adds physical details and checks timing with parasitics. Floorplanning places blocks, placement assigns cell locations, and routing connects cells and blocks. Circuit extraction determines resistances and capacitances, and post-layout simulation verifies functionality and timing.

BiCMOS Technology

BiCMOS TechnologyMithileysh Sathiyanarayanan The document discusses a technical seminar on BiCMOS technology. It begins with an introduction and describes the characteristics and fabrication processes of CMOS, bipolar, and BiCMOS technologies. BiCMOS combines the advantages of CMOS, like low power and high density, with bipolar's high speed and current drive. While more complex than CMOS, BiCMOS provides improved performance over both CMOS and bipolar. The document outlines the advantages and applications of BiCMOS, such as mixed-signal integrated circuits, and compares it to CMOS and bipolar technologies. It concludes with a literature survey on books and websites relating to BiCMOS design.

Pipelining approach

Pipelining approachGopinathD17 This document discusses pipelining as an approach to optimize sequential circuits. It describes how pipelining can be implemented using registers between logic blocks to improve resource utilization and increase throughput. This allows computations to be spread over multiple clock cycles in an assembly-line fashion. The document also discusses latch-based vs register-based pipelines and different logic styles like NORA-CMOS that can be used for pipelined structures. It covers design rules and considerations for ensuring correct pipelined operation. Finally, it briefly describes non-bistable sequential circuits like astable, monostable and Schmitt trigger circuits.

System on Chip (SoC)

System on Chip (SoC)Dimas Ruliandi Introduction to system on chip. Present some information about design, architecture and application of SoC

fpga programming

fpga programmingAnish Gupta This document discusses the programming technologies and interconnect architectures used in different FPGA devices. It covers antifuse-based OTP technologies used in Actel FPGAs, SRAM-based reprogrammable technologies used in Xilinx FPGAs, and EPROM/EEPROM technologies used in Altera CPLDs. It also describes the segmented channel routing interconnect architecture used in Actel FPGAs and the LCA architecture used in Xilinx FPGAs.

current mirrors

current mirrorsMallavarapu Mounika This document presents a new CMOS voltage divider based current mirror and compares it to basic and cascode current mirrors. The basic current mirror has limitations like finite output resistance and channel length modulation effects. The cascode current mirror improves output resistance but wastes threshold voltage. The new CMOS voltage divider current mirror uses an NMOS and PMOS transistor voltage divider to bias an NMOS transistor and control the output current. It consumes less power than the basic current mirror and is well-suited for low current biasing applications.

FPGA

FPGAAbhilash Nair This document discusses field programmable gate arrays (FPGAs). It begins by describing FPGA basics and architecture, including configurable logic blocks (CLBs), I/O blocks, and switch matrices. It then discusses FPGA advantages such as low cost, fast prototyping, and reusability. The document also covers FPGA process technologies including SRAM, antifuse, and EPROM/EEPROM/Flash. It provides details on FPGA architectures, logic elements, routing, memory blocks, and examples of Xilinx FPGAs.

basic vlsi ppt

basic vlsi pptSidduzalaki143 This document provides an overview of VLSI (Very Large Scale Integration) and its applications. It discusses the history of integrated circuits from their inception in the late 1940s to today's advanced nanoscale technologies. Key topics covered include Moore's law of transistor scaling, digital circuit design challenges, CMOS fabrication processes, and examples of how VLSI is used in various electronic systems and devices.

SOC design

SOC design Vinchipsytm Vlsitraining This document provides an overview of system on chip (SoC) design. It discusses that a SoC integrates all components of an electronic system onto a single chip, including digital, analog and radio frequency functions. The SoC design process involves identifying user needs and integrating various intellectual property blocks. It describes the SoC design flow, fundamentals like using soft and hard IP cores, and considerations like architecture strategy and validation. Key aspects covered include SoC architecture, on-chip buses to connect IP cores, and examples of commercial SoCs.

Pass Transistor Logic

Pass Transistor LogicSudhanshu Janwadkar This presentation discusses the basics of Pass Transistor Logic, its advantages, limitation and finally implementation of Boolean functions/Combinational Logic circuits using Pass Transistor Logic.

Pic microcontroller architecture

Pic microcontroller architectureDominicHendry The PIC microcontroller uses a Harvard architecture with separate program and data memories. It has a CPU with an ALU, memory unit, and control unit. The memory includes program memory to store instructions, data memory including registers for temporary data storage, and EEPROM for storing variables. It has advantages like a small instruction set, low cost, and built-in interfaces like I2C, SPI, and analog components.

ASIC Design Flow | Physical Design | VLSI

ASIC Design Flow | Physical Design | VLSI Jayant Suthar This document provides an overview of the ASIC design process, which includes the following main steps:

1. Front-end design including market research, specification, architecture, and RTL design.

2. Verification of the RTL code by verification engineers.

3. Synthesis of the RTL code into a gate-level netlist, followed by equivalence checking.

4. Physical design including placement and routing of standard cells, followed by extraction of parasitic components and timing analysis.

5. Physical verification including design rule checking and layout vs schematic checking.

Gate Diffusion Input Technology (Very Large Scale Integration)

Gate Diffusion Input Technology (Very Large Scale Integration)Ashwin Shroff The aim of project is by using GDI technique the power consumption, delay, chip area and connection and parasitic capacitors is decreased. In this project, we are implementing the new T-flip flop using GDI technique for low power and high speed in order to achieve power delay product (PDP)

Gdi cell

Gdi cellshipra_mishra This document presents a study comparing different circuit designs for a 1-bit full adder cell, including CMOS, CPL, DPL, and a novel GDI technique. It finds that the GDI technique can reduce power consumption, propagation delay, transistor count, and area compared to conventional CMOS and other pass-transistor logic designs. Schematics and layouts are presented for XOR/XNOR-based full adders implemented using the GDI technique. Simulation results show improvements in area, power, delay, and power-delay product compared to CPL and DPL designs. The GDI technique is concluded to be an effective low-power alternative for digital circuit design.

Ad

More Related Content

What's hot (20)

Switch level modeling

Switch level modelingDevi Pradeep Podugu This document discusses switch level modeling in Verilog. It describes different types of transistor switches that can be used as primitives in Verilog, including nmos, pmos, rnmos, rpmos, and cmos switches. It also covers bidirectional switches like tran, tranif1, and examples of how to use the switches to model basic logic gates and memory cells like a RAM cell. Time delays can be specified for switches. Switch level modeling allows designing circuits using transistors directly in Verilog.

TMS320C5x

TMS320C5xDeekshithaReddy23 The TMS320C5x DSP architecture is based on the C25 with some enhancements. It uses a Harvard architecture with separate program and data memory buses. The CPU contains a CALU for arithmetic, PLU for logic, and ARAU for address calculations. On-chip memory includes ROM, DARAM, and SARAM. Peripherals include serial ports, timers, interrupts, and I/O. The architecture provides high performance with low power consumption and compatibility with prior C series DSPs.

VLSI subsystem design processes and illustration

VLSI subsystem design processes and illustrationVishal kakade This document discusses the design processes for digital subsystem design. It begins by outlining the objectives of design consideration, problem and solution, basic digital processor structure, and datapath. It then discusses general considerations for subsystem design such as lower unit cost and higher reliability. It presents some common problems in design like how to design complex systems efficiently. It proposes solutions like top-down design and partitioning the system. The document then illustrates the design processes through examples like designing a 4-bit shifter and ALU subsystem. It provides block diagrams, logic diagrams and layouts at different stages of the design process.

Introduction to Embedded Systems I: Chapter 2 (1st portion)

Introduction to Embedded Systems I: Chapter 2 (1st portion)Moe Moe Myint The document provides an introduction to embedded systems and covers several topics:

- The core components of embedded systems including microprocessors, microcontrollers, digital signal processors, programmable logic devices, and commercial off-the-shelf components.

- Memory technologies used in embedded systems such as ROM, RAM, and flash memory.

- Sensors, actuators, and interfacing components like LEDs, displays, and motors.

- Communication interfaces including I2C, SPI, UART, and wireless standards.

- Other system components like reset circuits, oscillators, and watchdog timers.

- PCBs and their role in embedded design.

The document aims to provide learning objectives on the building

CMOS fabrication n well process

CMOS fabrication n well processSouvikDatta22 CMOS fabrication using n-well process: This is an industrial process used for making a CMOS inverter circuit.

ASIC

ASICGourab Palui This document provides an overview of application specific integrated circuits (ASICs). It discusses the main types of ASICs including full custom, semi-custom (standard cell-based and gate array-based), and programmable. For semi-custom, it describes standard cell-based ASICs using predesigned logic cells and different types of gate arrays including channeled, channelless, and structured. The document also covers the design flow, economics, merits like improved speed and power consumption, and demirts such as high costs for redesigns.

Logic Synthesis

Logic SynthesisVandanaPagar1 Logic synthesis is the process of converting a high-level design description into an optimized gate-level representation using a standard cell library and design constraints. The process involves translating the RTL description into an unoptimized internal representation, optimizing the logic, technology mapping, and producing an optimized gate-level netlist. An example logic synthesis flow is described for a 4-bit magnitude comparator design from RTL to optimized gates.

ARM7-ARCHITECTURE

ARM7-ARCHITECTURE Dr.YNM This class notes is meant for Electronics students of SKU and RU and also for ECE students of other universities.

Asic design flow

Asic design flowyogeshwaran k The document describes the ASIC design flow, which consists of two main phases: logical design (frontend) and physical design (backend).

The logical design phase includes design entry, logic synthesis, system partitioning, and pre-layout simulation. This phase converts the design from HDL or schematic to a netlist.

The physical design phase includes floorplanning, placement, routing, circuit extraction, and post-layout simulation. This phase adds physical details and checks timing with parasitics. Floorplanning places blocks, placement assigns cell locations, and routing connects cells and blocks. Circuit extraction determines resistances and capacitances, and post-layout simulation verifies functionality and timing.

BiCMOS Technology

BiCMOS TechnologyMithileysh Sathiyanarayanan The document discusses a technical seminar on BiCMOS technology. It begins with an introduction and describes the characteristics and fabrication processes of CMOS, bipolar, and BiCMOS technologies. BiCMOS combines the advantages of CMOS, like low power and high density, with bipolar's high speed and current drive. While more complex than CMOS, BiCMOS provides improved performance over both CMOS and bipolar. The document outlines the advantages and applications of BiCMOS, such as mixed-signal integrated circuits, and compares it to CMOS and bipolar technologies. It concludes with a literature survey on books and websites relating to BiCMOS design.

Pipelining approach

Pipelining approachGopinathD17 This document discusses pipelining as an approach to optimize sequential circuits. It describes how pipelining can be implemented using registers between logic blocks to improve resource utilization and increase throughput. This allows computations to be spread over multiple clock cycles in an assembly-line fashion. The document also discusses latch-based vs register-based pipelines and different logic styles like NORA-CMOS that can be used for pipelined structures. It covers design rules and considerations for ensuring correct pipelined operation. Finally, it briefly describes non-bistable sequential circuits like astable, monostable and Schmitt trigger circuits.

System on Chip (SoC)

System on Chip (SoC)Dimas Ruliandi Introduction to system on chip. Present some information about design, architecture and application of SoC

fpga programming

fpga programmingAnish Gupta This document discusses the programming technologies and interconnect architectures used in different FPGA devices. It covers antifuse-based OTP technologies used in Actel FPGAs, SRAM-based reprogrammable technologies used in Xilinx FPGAs, and EPROM/EEPROM technologies used in Altera CPLDs. It also describes the segmented channel routing interconnect architecture used in Actel FPGAs and the LCA architecture used in Xilinx FPGAs.

current mirrors

current mirrorsMallavarapu Mounika This document presents a new CMOS voltage divider based current mirror and compares it to basic and cascode current mirrors. The basic current mirror has limitations like finite output resistance and channel length modulation effects. The cascode current mirror improves output resistance but wastes threshold voltage. The new CMOS voltage divider current mirror uses an NMOS and PMOS transistor voltage divider to bias an NMOS transistor and control the output current. It consumes less power than the basic current mirror and is well-suited for low current biasing applications.

FPGA

FPGAAbhilash Nair This document discusses field programmable gate arrays (FPGAs). It begins by describing FPGA basics and architecture, including configurable logic blocks (CLBs), I/O blocks, and switch matrices. It then discusses FPGA advantages such as low cost, fast prototyping, and reusability. The document also covers FPGA process technologies including SRAM, antifuse, and EPROM/EEPROM/Flash. It provides details on FPGA architectures, logic elements, routing, memory blocks, and examples of Xilinx FPGAs.

basic vlsi ppt

basic vlsi pptSidduzalaki143 This document provides an overview of VLSI (Very Large Scale Integration) and its applications. It discusses the history of integrated circuits from their inception in the late 1940s to today's advanced nanoscale technologies. Key topics covered include Moore's law of transistor scaling, digital circuit design challenges, CMOS fabrication processes, and examples of how VLSI is used in various electronic systems and devices.

SOC design

SOC design Vinchipsytm Vlsitraining This document provides an overview of system on chip (SoC) design. It discusses that a SoC integrates all components of an electronic system onto a single chip, including digital, analog and radio frequency functions. The SoC design process involves identifying user needs and integrating various intellectual property blocks. It describes the SoC design flow, fundamentals like using soft and hard IP cores, and considerations like architecture strategy and validation. Key aspects covered include SoC architecture, on-chip buses to connect IP cores, and examples of commercial SoCs.

Pass Transistor Logic

Pass Transistor LogicSudhanshu Janwadkar This presentation discusses the basics of Pass Transistor Logic, its advantages, limitation and finally implementation of Boolean functions/Combinational Logic circuits using Pass Transistor Logic.

Pic microcontroller architecture

Pic microcontroller architectureDominicHendry The PIC microcontroller uses a Harvard architecture with separate program and data memories. It has a CPU with an ALU, memory unit, and control unit. The memory includes program memory to store instructions, data memory including registers for temporary data storage, and EEPROM for storing variables. It has advantages like a small instruction set, low cost, and built-in interfaces like I2C, SPI, and analog components.

ASIC Design Flow | Physical Design | VLSI

ASIC Design Flow | Physical Design | VLSI Jayant Suthar This document provides an overview of the ASIC design process, which includes the following main steps:

1. Front-end design including market research, specification, architecture, and RTL design.

2. Verification of the RTL code by verification engineers.

3. Synthesis of the RTL code into a gate-level netlist, followed by equivalence checking.

4. Physical design including placement and routing of standard cells, followed by extraction of parasitic components and timing analysis.

5. Physical verification including design rule checking and layout vs schematic checking.

Viewers also liked (20)

Gate Diffusion Input Technology (Very Large Scale Integration)

Gate Diffusion Input Technology (Very Large Scale Integration)Ashwin Shroff The aim of project is by using GDI technique the power consumption, delay, chip area and connection and parasitic capacitors is decreased. In this project, we are implementing the new T-flip flop using GDI technique for low power and high speed in order to achieve power delay product (PDP)

Gdi cell

Gdi cellshipra_mishra This document presents a study comparing different circuit designs for a 1-bit full adder cell, including CMOS, CPL, DPL, and a novel GDI technique. It finds that the GDI technique can reduce power consumption, propagation delay, transistor count, and area compared to conventional CMOS and other pass-transistor logic designs. Schematics and layouts are presented for XOR/XNOR-based full adders implemented using the GDI technique. Simulation results show improvements in area, power, delay, and power-delay product compared to CPL and DPL designs. The GDI technique is concluded to be an effective low-power alternative for digital circuit design.

Digital Electronics( half adders and full adders)

Digital Electronics( half adders and full adders)Bosa Theophilus Ntshole This document describes a laboratory experiment on logic gates and combinational circuits conducted by students at the University of Botswana. The aim was to introduce half adders and full adders. Students used AND, OR, and XOR gates to build the circuits on a breadboard. Their results matched the theoretical truth tables. Issues arose due to crowded workspaces and old equipment. Recommendations included upgrading equipment and better preparation by students. The conclusion was that practical observations matched expectations, demonstrating an understanding of combinational circuit design.

CSLA and WTM using GDI Technique

CSLA and WTM using GDI TechniqueNishant Yaduvanshi Designing of Carry select adder and wallace tree multiplier using Gate diffusion Input technique by which area and power consumption is reduced.

Low power vlsi design ppt

Low power vlsi design pptAnil Yadav Low power VLSI design has become an important discipline due to increasing device densities, operating frequencies, and proliferation of portable electronics. Power dissipation, which was previously neglected, is now a primary design constraint. There are several sources of power dissipation in CMOS circuits, including switching power due to charging and discharging capacitances, short-circuit power during signal transitions, and leakage power from subthreshold and gate leakage currents. Designers have some control over power consumption by optimizing factors such as activity levels, clock frequency, supply voltage, transistor sizing and architecture.

Design half ,full Adder and Subtractor

Design half ,full Adder and Subtractor[email protected]. This document describes the design and operation of half adders, full adders, half subtractors, and full subtractors. It defines each component, provides their truth tables, and shows how to design the logic circuits using K-maps. Half adders and subtractors perform addition and subtraction of two single bits, while full adders and subtractors handle three input bits, accounting for values carried in and out. The document also distinguishes between the components and their uses in digital logic systems.

Half adder & full adder

Half adder & full adderGaditek Group members for the project are Falah Hassan, Maidah Malik, and Maria Khan. The document discusses half adders and full adders. A half adder adds two binary digits and produces a sum and carry output. It is built from two logic gates. A full adder accepts two input bits and a carry input, and produces a sum and carry output. It is implemented using two half adders joined by an OR gate. The main difference between a half adder and full adder is that a full adder has three inputs and two outputs, allowing multiple adders to be chained to add more bits.

My Report on adders

My Report on addersPeeyush Pashine The document discusses various types of adders including 1-bit adders like half adders and full adders, multi-bit adders like ripple carry adders, carry lookahead adders, carry select/skip adders, and carry save adders. It provides details on the design, pros and cons, and Verilog code for each type of adder. The document aims to provide a comparative study of these adders through detailed analysis and descriptions.

A report on 2 to 1 mux using tg

A report on 2 to 1 mux using tgvijay rastogi A transmission gate is similar to a relay that can conduct in both directions or block by a control signal with almost any voltage potential. CMOS transmission gate consists of one nMOS and one pMOS transistor, connected in parallel. The gate voltages applied to these two transistors are also set to be complementary signals. As such, the CMOS TG operates as a bidirectional switch between the nodes A and B which is controlled by signal C

4 bit cmos full adder in submicron technology with low leakage and groun...

4 bit cmos full adder in submicron technology with low leakage and groun...shireesha pallepati This document describes a proposed 4-bit CMOS full adder design with techniques to reduce leakage power and ground bounce noise. It introduces sleep transistors to improve upon conventional CMOS full adder designs. Simulation results show the modified design with sleep transistors reduces both standby leakage current and ground bounce noise compared to baseline designs without sleep transistors.

Ramya Project

Ramya ProjectRamya Purohit This document discusses the performance analysis of different CMOS full adder circuits and the VLSI design of a multiplier using Mentor Graphics. It analyzes the performance of various full adder circuits in terms of delay, power dissipation, and power-delay product. The high-performance 8T full adder is identified and used in the design of 4x4 multipliers like array, Braun, Baugh-Wooley, and Wallace tree multipliers. The multipliers are then analyzed and compared based on their complexity and performance.

Project report on design & implementation of high speed carry select adder

Project report on design & implementation of high speed carry select adderssingh7603 This document provides a table of contents for a thesis on improving carry select adders. It outlines that Chapter 1 provides an introduction and motivation for reducing area, delay, and power consumption in carry select adders. Chapter 2 presents a literature review on techniques used to optimize parameters like area, delay, and power. Chapter 3 describes different types of adders used as building blocks in carry select adders, including half adders, full adders, and ripple carry adders. Chapters 4-5 present the methodology and results for implementing various carry select adder designs using different techniques to reduce costs.

Adder ppt

Adder pptAvinash Jadhav This document discusses different types of digital adders. It defines an adder as a digital circuit that performs addition of numbers. It describes half adders, full adders, ripple carry adders, and look ahead carry units. For half adders, it provides the logic equations for sum and carry outputs. For full adders, it gives the logic equations for sum and carry outputs and includes the truth table. It explains that ripple carry adders use multiple full adders in sequence to add N-bit numbers, with each carry bit "ripplying" to the next full adder.

Explain Half Adder and Full Adder with Truth Table

Explain Half Adder and Full Adder with Truth Tableelprocus An adder is a digital logic circuit in electronics that implements addition of numbers. In many computers and other types of processors, adders are used to calculate addresses, similar operations and table indices in the ALU and also in other parts of the processors. These can be built for many numerical representations like excess-3 or binary coded decimal.

Design a Low Power High Speed Full Adder Using AVL Technique Based on CMOS Na...

Design a Low Power High Speed Full Adder Using AVL Technique Based on CMOS Na...IOSR Journals Abstract: Power and delay optimization is a very crucial issue in low voltage applications. In this paper, we present a design of Full Adder circuit using AVL techniques for low power operation. The approach for the design is based on XOR/XNOR & Transmission gate for single bit as hybrid design .By using this approach Full Adder is being designed using 12 transistors. We can reduce the value of total power dissipation by applying the AVLG (adaptive voltage level at ground) technology in which the ground potential is raised and AVLS (adaptive voltage level at supply) in which supply potential is increased. The main aim of the design is to investigate the power, Propagation Delay and Power delay Product for low voltage Full Adder for the proposed design style. The simulation results show that there is a significant reduction in power consumption for this proposed cell with the AVL technique. The circuit is designed using 65 nanometer CMOS technology and simulated using MicroWind and DSCH Ver. 3.1 Keywords: Full Adder, AVL Techniques, Low Power, VLSI, High Performance

35th 36th Lecture

35th 36th Lecturebabak danyal This document discusses the design and operation of arithmetic logic units (ALUs) and different types of adders used in ALUs, including ripple carry adders and carry look-ahead adders. It explains that a ripple carry adder has carry propagation delay as its limiting factor, while a carry look-ahead adder calculates carry signals in advance to reduce delay. The carry look-ahead adder uses generate and propagate signals to express carry outputs without relying on preceding carry signals, allowing it to provide sum outputs several gates faster than a ripple carry adder. Verilog code is also presented for implementing a carry look-ahead adder.

Performance Analysis of Full Adder Based 2- Bit Comparator using Different De...

Performance Analysis of Full Adder Based 2- Bit Comparator using Different De...IJEEE This document presents a performance analysis of different design approaches for a 2-bit comparator circuit based on a full adder module. Three logic styles are evaluated: CMOS logic, Pass Transistor Logic (PTL), and Gate Diffusion Input (GDI) logic. The 2-bit comparator circuit is designed and simulated using each logic style at both 45nm and 90nm process technologies. Simulation results show that the PTL-based comparator has the smallest area of the three designs. In terms of power consumption, PTL performs best at lower voltages below 1.4V, while GDI consumes the least power above 1.4V. Overall, the PTL logic style provides the best trade-off between area

Layout Design of Low Power Half Adder using 90nm Technology

Layout Design of Low Power Half Adder using 90nm Technology IJEEE The basic building block of any digital operation is addition. This paper compares fully automatic and proposed semicustom layout design; the proposed design has been optimized for power consumption, low area and high speed. Power consumption and area are the major design issue for a designer. All the design result of fully custom and proposed semicustom design taken at 1.2V. In this the circuit simulation has been done on DSCH3 and layout simulation on Microwind3.1.

Ieee project reversible logic gates by_amit

Ieee project reversible logic gates by_amitAmith Bhonsle 1) The document presents designs for reversible logic gates and their applications in low power circuits. It proposes an improved design for a reversible programmable logic array (RPLA) using multiplexer and Feynman gates that is more efficient than existing designs.

2) It also proposes a method for structuring a reversible arithmetic logic unit (ALU) using reversible logic gates instead of traditional gates, achieving the same functionality with reduced information loss.

3) The RPLA design is demonstrated by implementing reversible 1-bit full adders and subtractors. Simulation results show the proposed design optimizes the number of reversible gates used.

Ad

Similar to Implementation of 1 bit full adder using gate diffusion input (gdi) technique (20)

Chapter 10.pptx

Chapter 10.pptxWaleedHussain30 This document provides an overview of digital CMOS logic circuits. It discusses CMOS technology and how it has become the dominant technology for digital circuit implementation due to its low power dissipation and high integration density. The document then covers different logic circuit families including CMOS, bipolar, BiCMOS, and GaAs. It discusses characteristics of logic circuits like noise margins, propagation delay, power dissipation, silicon area, and fan-in/fan-out. Different digital system design styles using off-the-shelf components or custom VLSI chips are presented. The role of design abstraction and computer aids in facilitating large digital system design is also covered. Finally, the document discusses CMOS inverter circuit operation and the voltage transfer

Low power

Low powerpreeti banra The document discusses various techniques for reducing power consumption at different levels, from circuit-level optimizations like transistor sizing and voltage scaling, to logic synthesis techniques like clock gating and state encoding, to algorithm-level optimizations and architecturally-static pipelining supported by an optimizing compiler. It notes that power optimization is important for cost, dependability, and extending battery life, and that while proposed approaches show potential, accurate energy assessments of new techniques are still needed.

design and implementation of Area efficient arithmetic circuit

design and implementation of Area efficient arithmetic circuitSravanKumar743222 PPT regarding Project Base Paper

CMOS Logic Circuits

CMOS Logic CircuitsMarmik Kothari This document discusses CMOS logic circuits. It begins by defining logic values and how bits are encoded using voltage levels. It then discusses different logic gates like inverters, NAND, NOR and buffers. It explains that logic gates are made from MOS transistors and describes the characteristics of N-type and P-type MOSFETs. The rest of the document discusses various electrical characteristics of CMOS logic circuits like logic levels, noise margins, input/output currents, fan-in, fan-out, propagation delay and power consumption. It also briefly mentions different CMOS logic families and issues around interfacing CMOS and TTL logic standards.

Power dissipation cmos

Power dissipation cmosRajesh Tiwary This document discusses power dissipation in CMOS circuits. It identifies the main sources of power dissipation as dynamic, static, and short circuit power. Dynamic power is caused by charging and discharging capacitors during switching and depends on activity factors, voltage, and frequency. Static power includes leakage currents that occur even when the device is inactive. Short circuit power arises when both NMOS and PMOS are on simultaneously during signal transitions. The document provides techniques for reducing each type of power dissipation such as lowering voltage, reducing switching activity, minimizing capacitance and transistor sizing.

Basics of ATmega32

Basics of ATmega32Nima Ghaedsharafi The document provides an overview of the ATMega32 microcontroller. It describes the microcontroller's key features which include being 8-bit, low-power, and having 32Kbytes of programmable flash memory. It also outlines the microcontroller's ports, power sources, and oscillator options. Programming tools that can be used with the ATMega32 like various compilers and hardware programmers are also listed.

Study on self resetting logic with gate diffusion input (SRL-GDI)

Study on self resetting logic with gate diffusion input (SRL-GDI)shubham jha

With continual technology scaling and improvements in lithography, the integrated system has become faster and thus it is employed in diverse real-time applications. To support high performance applications, proper choice of technology selection and topology for implementing various logic are the mandatory issues in designing low- power devices.

Self Resetting Logic with Gate Diffusion Input (SRLGDI) is the successor of SRCMOS where the CMOS block is replaced with the GDI block hence the name SRLGDI, which is an asynchronous dynamic circuit. This logic family resolves the issues in dynamic circuits like charge sharing , charge leakage , short circuit power dissipation, monotonicity requirement and low output voltage.

In this design the pull down tree is implemented with gate diffusion input (GDI) with level restoration which apparently eliminates the conductance overlap between nMOS and pMOS devices , thereby reducing the short circuit power dissipation and providing high output voltage.

CMOS Topic 6 -_designing_combinational_logic_circuits

CMOS Topic 6 -_designing_combinational_logic_circuitsIkhwan_Fakrudin This document discusses designing combinational logic circuits using static complementary CMOS design. It explains how to construct static CMOS circuits for logic gates like NAND and NOR by using pull-up and pull-down networks of PMOS and NMOS transistors respectively. Issues related to pass-transistor design like noise margins and static power consumption are also covered. The document provides details on implementing various logic functions using pass-transistor logic and differential pass-transistor logic. It discusses solutions to overcome the disadvantages of pass-transistor logic like level restoration and use of multiple threshold transistors.

Summary Of Course Projects

Summary Of Course Projectsawan2008 This document summarizes several course projects completed by Setiawan Soekamtoputra for their Master's degree. The projects include:

1) Design of a 32-bit pipelined CPU in Verilog including implementation of an ASIC flow, multiplier with accumulator case study, and pipeline optimization case study.

2) Development of a monitor program for the MC68000 processor in assembly language including common memory and register commands and exception handlers.

3) Implementation of a high-performance pipelined MIPS processor in VHDL including hazard detection and data forwarding units to handle data and branch hazards.

4) Network on chip prototype designs including a 3-node partially connected mesh design in SystemC and

UNIT-4-Logic styles for low power_part_2.ppt

UNIT-4-Logic styles for low power_part_2.pptRavi Selvaraj There are two approaches to realize digital circuits using MOS technology: gate logic and switch logic. Gate logic uses inverters and gates like NAND and NOR, while switch logic uses pass transistors. There are also two types of gates - static and dynamic. Static gates do not need a clock, while dynamic gates use intrinsic capacitors that must be refreshed regularly to avoid information loss. The document discusses three logic styles for low power design: static CMOS logic, dynamic CMOS logic, and pass transistor logic (PTL), outlining their advantages and disadvantages in area, power, speed, and complexity.

ICIECA 2014 Paper 23

ICIECA 2014 Paper 23Association of Scientists, Developers and Faculties The document compares double gate MOSFETs to single gate MOSFETs. Double gate MOSFETs reduce leakage current and delay compared to single gate by controlling the silicon channel more efficiently with two gates. This improves short channel effects and leads to higher currents. Double gate MOSFETs are suitable for low power and high performance applications due to their reduced leakage current and improved device characteristics like reduced short channel effects and improved current driving capability.

Combinational MOS Logic Design (Combinational Metal oxide semiconductor logic...

Combinational MOS Logic Design (Combinational Metal oxide semiconductor logic...AmitKumar571646 Presentation on combinational mosfet logic designs. Basic introduction, examples, pass transistor logic etc

02_Cornelsen_Doug_mapld09_pres_1.ppt

02_Cornelsen_Doug_mapld09_pres_1.pptssuserf2cc17 This document describes the implementation of a sigma delta analog-to-digital converter (ADC) design in an FPGA. It discusses the motivation to use an FPGA-based design instead of a traditional radiation-hardened ADC. The design constraints and process are described, including using MATLAB to design filters, simulating the design, and hand coding the filters in VHDL. Preliminary test results on a prototype show the design meets the accuracy goals and is viable to prototype further.

EMBEDDED SYSTEM BASICS

EMBEDDED SYSTEM BASICSRANAALIMAJEEDRAJPUT BY VIEWING THIS SLIDES YOU ABLE TO KNOW

-WHAT IS EMBEDDED SYSTEM?

-WHAT ARE PROS AND CONS OF EMBEDDED SYSTEM?

-WHERE IT IS USED?

-WHAT IS FGPA,MICROPROCESSOR,CRYPTOGRAPHY,JTAG,SPI, SERIAL AND PARALLEL COMMUNICATION?

AND MUCH MORE.

basic_CMOS_technology_CERN_GENEVA_SWITZERLAND.ppt

basic_CMOS_technology_CERN_GENEVA_SWITZERLAND.pptlefohi9060 A comprehensive slideshow of ASIC design and CMOS technology

Ad

More from Grace Abraham (7)

Maha an energy efficient malleable hardware accelerator for data intensive a...

Maha an energy efficient malleable hardware accelerator for data intensive a...Grace Abraham This document describes a Malleable Hardware Accelerator (MAHA) for data intensive applications. MAHA implements a reconfigurable computing fabric within off-chip memory to enable computation within the memory. It presents modifications made to a NAND flash memory architecture to realize the MAHA framework, including adding control logic and custom datapaths to memory blocks. It also describes the software architecture for mapping applications to MAHA, including decomposing and fusing operations. Evaluation results show the area and energy overhead of MAHA and performance/energy improvements when mapping applications compared to a general-purpose processor.

Embedded system hardware architecture ii

Embedded system hardware architecture iiGrace Abraham This document discusses several topics related to embedded system hardware and software design including electrostatic discharge effects, fault tolerance techniques, hardware development tools, software development tools, thermal analysis and design considerations for battery-powered systems. It also covers processor performance metrics like instructions per second, operations per second, and benchmarks.

Design and implementation of cmos rail to-rail operational amplifiers

Design and implementation of cmos rail to-rail operational amplifiersGrace Abraham This document discusses the design of rail-to-rail operational amplifiers. It covers rail-to-rail input and output stages, schematic design considerations, layout implementation, simulation results, and conclusions. Specifically, it evaluates different input stage topologies including complementary differential pairs with active loads or cascode loads. For the output stage, it examines push-pull inverters or common source configurations. The document concludes that a complementary differential pair with cascode load as the input stage and a push-pull inverter as the output stage achieves maximum gain while minimizing stability issues and output voltage swing limitations.

Clock recovery in mesochronous systems and pleisochronous systems

Clock recovery in mesochronous systems and pleisochronous systemsGrace Abraham This document discusses clock recovery in mesochronous and pleisochronous systems. For mesochronous systems, where the clock and data have the same frequency but unknown phase, clock recovery loops use phase detectors like Hogge or Alexander detectors to calibrate only the phase of the incoming clock. For pleisochronous systems, where the clock frequency can also have a small error, phase-locked loops with phase-frequency detectors are used to first lock the voltage-controlled oscillator frequency to a reference and then switch to tracking the data timing.

MEMS ACCELEROMETER BASED NONSPECIFIC – USER HAND GESTURE RECOGNITION

MEMS ACCELEROMETER BASED NONSPECIFIC – USER HAND GESTURE RECOGNITIONGrace Abraham The document describes a MEMS accelerometer-based system for recognizing nonspecific user hand gestures. It analyzes gesture motion using a 3-axis accelerometer and develops three models for gesture recognition: 1) based on sign sequence and a Hopfield network, 2) based on velocity increment comparisons, and 3) based on sign sequence and template matching. The third model achieved the highest accuracy of 95.6% in experiments. Potential applications include controlling devices with hand gestures.

Rtl design optimizations and tradeoffs

Rtl design optimizations and tradeoffsGrace Abraham This document discusses several optimizations and tradeoffs that can be made during RTL design of datapaths, including pipelining, concurrency, component allocation, operator binding, and operator scheduling. It provides examples of applying these techniques to optimize designs for FIR filters and SAD computation. Additionally, it discusses a multiple clocking scheme for low-power RTL design and an input space adaptive design methodology for optimizing energy and performance.

A 128 kbit sram with an embedded energy monitoring circuit and sense amplifie...

A 128 kbit sram with an embedded energy monitoring circuit and sense amplifie...Grace Abraham The document describes a 128 Kbit SRAM with an embedded energy monitoring circuit. It uses an 8T bit cell to enable low voltage operation down to 0.37V. It employs a two-stage sensing scheme using a body-biased sense amplifier to compensate for offsets. An energy monitoring circuit is integrated to measure the absolute energy consumption of the SRAM. It functions down to low voltages while achieving improved read performance and accurate energy measurement.

Implementation of 1 bit full adder using gate diffusion input (gdi) technique

- 1. WELCOME

- 2. GRACE ABRAHAM ROLL . NO : 01 S1 MTECH VLSI & ES FISAT IMPLEMENTATION OF 1-BIT FULL ADDER USING GATE DIFFUSION INPUT (GDI) TECHNIQUE 2

- 3. CONTENTS • INTRODUCTION • ADVANTAGES OF GDI OVER CMOS TECHNOLOGY • BASIC GDI CELL FUNCTIONS • TRANSIENT ANALYSIS OF BASIC GDI FUNCTIONS • OPERATIONAL ANALYSIS • COMPARISION WITH CMOS LOGIC STYLES • CONVENTIONAL CMOS 1-BIT FULL ADDER • XOR BASED FULL ADDER • GDI 1-BIT FULL ADDER • CONCLUSION 3

- 4. INTRODUCTION • VLSI application use arithmetic operations • Logic gates are building blocks of digital circuits • 1-bit full adder cell used in arithmetic circuits • Enhancing the performance is critical • Low power VLSI systems is highly in demand • Designers are faced with more constraints • Main aim is to minimize the power consumption Low power High speed Small silicon area High throughput 4

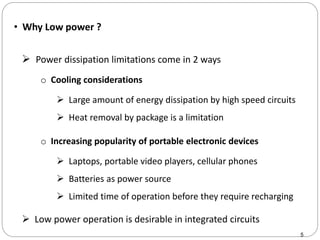

- 5. • Why Low power ? 5 Power dissipation limitations come in 2 ways Low power operation is desirable in integrated circuits o Cooling considerations Large amount of energy dissipation by high speed circuits Heat removal by package is a limitation o Increasing popularity of portable electronic devices Laptops, portable video players, cellular phones Batteries as power source Limited time of operation before they require recharging

- 6. 6 ADVANTAGES OF GDI OVER CMOS • Low power circuit design • Allows reducing power consumption • Reducing propagation delay • Reducing area of digital circuit • Maintaining low complexity of logic design

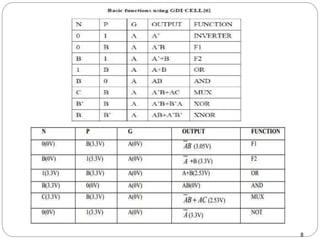

- 7. 7 BASIC GDI CELL FUNCTIONS • Reminds the standard CMOS inverter • Basic structure 3 inputs 1 output Bulk of both NMOS & PMOS are connected to N or P respectively o G (common gate input of NMOS & PMOS) o P (input to the source/drain of PMOS) o N (input to the source/drain of NMOS ) o D

- 8. 8

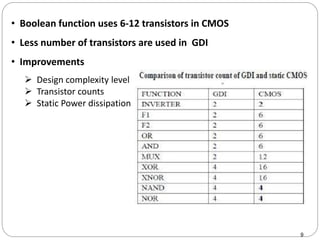

- 9. • Boolean function uses 6-12 transistors in CMOS • Less number of transistors are used in GDI • Improvements Design complexity level Transistor counts Static Power dissipation 9

- 10. TRANSIENT ANALYSIS OF BASIC GATE DIFFUSION INPUT (GDI) FUNCTIONS 10 • v(1) : Input voltage at G • v(2) : Input voltage at P • v(4) : Input voltage at N • v(3) : Output voltage at D

- 11. 11

- 12. 12

- 13. 13 OPERATIONAL ANALYSIS • Problem with pass transistor logic : low voltage swing • For function F1 • Low swing occurs in output when A=0 & B=0 • Expected Vtp = 0 v , due to poor high to low transition chara. of PMOS Vtp =.50v

- 14. 14 • Extra buffer circuitry may eliminate low voltage swing • About 50% of GDI cell operates as regular CMOS inverter • Used as a digital buffer for logic level restoration • In some cases, when VDD= 1 without a swing from the previous stages, a GDI functions as an inverter buffer and recovers the voltage swing

- 15. 15 COMPARISION WITH CMOS LOGIC STYLES • Circuits were designed in 0.35µm twin well CMOS technology • Simulated using AIMSPICE at 3.3V with load capacitance =100 fF

- 16. 16 • GDI have the lowest transistor count • Both power and delay are less in case of GDI technique

- 17. 17 CONVENTIONAL CMOS 1-BIT FULL ADDER • In VLSI application, arithmetic operations play important role • 1 bit full adder is building block of all operations • CMOS 1 bit full adder Addition Subtraction Multiplication Inputs : A, B, Cin (1 bit) Outputs : Sum, Carry (1 bit)

- 18. • CMOS design style is not area efficient for complex gates • CMOS full adder cell has 28 transistors • Pseudo NMOS • Dynamic logic • CMOS logic Static power consumption is high Compromise noise margin Charge leakage Charge sharing PMOS pull up & NMOS pull down network Number of transistors used is high o Requires frequent refreshing 18

- 19. 19

- 20. XOR BASED FULL ADDER • Equation obtained earlier can be modified as • Full adder can be implemented as 2 XOR gate and 1 mux using GDI cell 20

- 21. GDI CELL FOR XOR GATE • Only 4 transistors are used 21

- 22. GDI CELL FOR 1-BIT FULL ADDER • Built from two XOR gate and one MUX • Number of transistors used is reduced to 10 22

- 23. TRANSIENT ANALYSIS OF GDI BASED 1-BIT FULL ADDER • Inputs : v(1) –A, v(4)-B, v(7)-Cin • Outputs : v(8) – sum , v(9)- Cout 23

- 25. CONCLUSION • 2-Transistor implementation of complex logic functions • In-cell swing restoration under certain operating conditions • Low power design technique • New Circuit is most energy efficient cell compared to CMOS circuits • Issue of sequential logic design is currently being explored • Works are going on in automation of a logic design methodology on Gate Diffusion Input cells 25

- 26. REFERENCES • WEBSITES www.ijecse.org ieeexplore.ieee.org/ Implementation of 1-bit Full Adder using Gate Difuision Input (GDI) cell,Arun Prakash Singh 1, Rohit Kumar 2:1,Electronics and Communication Engineering Department, Northern India Engineering College,Lucknow, Uttar Pradesh, India.2.Electronics and Communication Engineering Department, Krishna Girls Engineering College A. Morgenshtein, A. Fish, I. A. Wagner,” Gate Diffusion Input (GDI) – A Novel Power Efficient Method for Digital Circuits: A Design Methodology”, 14th ASIC/SOC Conference, Washington D.C., USA, September 2001. and more.... • PAPERS REFERED 26

- 27. 27 THANK YOU 27