Ad

microprocessor and microcontroller material

- 1. 1 Department of Electrical and Electronics Engineering National Institute of Technology Puducherry, Karaikal-609 609 COMPUTER ORGANISATION AND MICROCONTROLLERS SUBJECT CODE: EE208 L T P C 3 0 2 5

- 2. Course Objectives 1. To provide the concept of computer architecture and mechanisms related to the design of processors, memories and networks. 2. To equip the students with a basic understanding of architecture, addressing modes instruction set, interrupt structure of 8051 microcontroller. 3. To familiarize commonly used interfacing ICs. 4. To develop skill for writing simple assembly language program using 8051 microcontroller. 2

- 3. Syllabus UNIT I FUNDAMENTAL PROCESSORS: Instruction set architecture; single-cycle, FSM and pipelined processor microarchitecture; resolving structural, data, control, and name hazards; and analyzing processor performance UNIT II FUNDAMENTAL MEMORIES: Memory technology; direct-mapped vs. associative caches; write-through and write-back caches; memory protection, translation, and virtualization; FSM and pipelined cache microarchitecture; analyzing memory performance; and integrating processors and memories UNIT III FUNDAMENTAL NETWORKS: Network topology and routing; buffer, channel, and router microarchitecture; analyzing network performance; and integrating processors, memories, and networks UNIT IV 8051 MICRO CONTROLLER: Functional block diagram - Instruction format and addressing modes – Instruction Set –Simple programs interrupt structure, Timer –I/O ports – Serial communication, Memory interfacing. UNIT V APPLICATIONS OF 8051 MICROCONTROLLER: Seven segment LED Display systems - Interfacing LCD Display - Stepper motor control - Interfacing A/D Converter –D/A Converter – Waveform generators - Generation of Gate signals. 3

- 4. BOOK 1: Computer Architecture: A Quantitative Approach (5th edition) John L Hennessy and David A Patterson Appendix A,B,C Book 2: Digital Design and Computer Architecture by David Money Harris and Sarah L. Harris Chapter 6,7,8, Appendix B 4

- 5. UNIT 1 FUNDAMENTAL PROCESSORS Instruction set architecture; single -cycle, FSM and pipelined processor microarchitecture; resolving structural, data, control, and name hazards; and analyzing processor performance 5

- 6. Introduction Computer: machine designed to process, store, and retrieve data Data? All data is stored in the computer as numbers. Interesting to know What are there inside the computer? How does it work? 6 Embedded Computer Desktop Computer

- 7. Embedded Computer 7 Embedded Computer: purpose-built computing platforms designed for a specific task or fixed functionality may be a single chip acting as simple controller for a garden-watering system may be a 150-processor, distributed parallel machine for flight systems of a jet

- 8. Historical Perspective 8 •Components<100 •Gates<10 SSI •Components<500 •10<Gates<100 MSI •500<Components<3 lakh •Gates>100 LSI •Components>3lakh VLSI •Components>1.5Cr ULSI •Billions of transistors on chip Pascaline (1642) Mechanical calculator Babbage Engine (2002) 8000 part, 5 tons, 11 ft length ENIAC 8,000 vacuum tubes, 30 tons, 30x50 ft Harvard Mark 1 (1944) mechanical relays, 35 tons, 500 miles of wiring IBM 360 (1960- 1970) Mainframe computer uses SLT Intel core i7 •Modern processor chip Mechanical relays Vacuum tubes Transistors Journey of miniaturization

- 10. Evolution of Computer Systems 10 Generation Main technology Representative System I (1945-54) Vacuum tubes, relays Machine/assembly language ENIAC, IBM701 II (1955-64) Transistor, memories, I/O processor HLL, Batch processing, IBM 7090 III (1965-74) SSI & MSI ICs, Microprogramming Multiprogramming/Time sharing OS, Intel 8008 IV (1975-84) LSI & VLSI ICs Multiprocessor Intel 8086, 8088 V (1984-90) VLSI, microprocessor on-chip Parallel Computing, Intel 486 VI (1990 onwards) ULSI, VHSIC, high density packaging, scalable architecture, post CMOS technologies Massively parallel processing/Pentium, Sun Ultra Workstation

- 11. Evolution of Computer Systems 11 Source: https://www.thediff.co/p/how-apple-can-own-io-to-own-the-universe Future? • Large scale IoT based system • Wearable computing • Intelligent Objects Source: Plouznikoff, et al (2007). Gesture-based interactions with virtually embodied wearable computer software processes competing for user attention. 2533-2538. 10.1109/ICSMC.2007.4414047.

- 12. Evolution of Computer Systems 12 Comparison of motherboard form factors ATX (Advanced Technology eXtended) is a motherboard and power supply configuration specification developed by Intel in 1995 Source: https://en.wikipedia.org/wiki/ATX 1995 1997 2001 2003 2008 2009

- 13. Evolution of Computer Systems 13 Moore’s law: • Moore's Law states that the number of transistors on a microchip doubles about every two years, though the cost of computers is halved. • In 1965, Gordon E. Moore, the co-founder of Intel, made this observation Source: https://www.cringely.com/2013/10/15/breaking-moores-law/

- 14. Computer Architecture: Trends 14 Application Requirements • Provide motivation for building system • SW/HW interface expressive yet productive Computer architects provide feedback to guide application and technology research directions Technology Constraints • Restrict what can be done efficiently • New technologies make new arch possible Computer engineering is the development of the abstraction/implementation layers that allow us to execute information processing applications efficiently using available manufacturing technologies Challenges in Single-Core Era

- 15. Computer Architecture: Trends 15 Application Requirements Energy and power constraints limit processor clock frequencies and the complexity of each core Computer architects address energy and power constraints by integrating multiple cores on a chip creating new software challenges Technology Constraints Multi-core processors require programmers to parallelize their software to take advantage of the multiple cores Challenges in Multi-Core Era

- 16. Computer Architecture: Trends 16 Application Requirements Accelerators require programmers to restructure their software to take advantage of the specialized hardware Computer architects address slower technology scaling by integrating multiple accelerators on a chip creating new software challenges Technology Constraints The slowing of Moore's law means general- purpose processors no longer provide significant application benefit Challenges in Accelerator Era

- 17. Computer Architecture: Trends 17 Single Core Era Multi Core Era Accelerator Era

- 18. Computer System Application Software Algorithm Programming Language Operating System Compiler Instruction set architecture Microarchitecture Register Transfer Level Gate level (logic) Circuits Devices Physics/Technology 18 Computer Architecture Sort array of numbers: 2,5,7,3,6->> 2,3,5,6,7 Selection of sort algorithm: 1. Find min no. in array 2. Move min no. to o/p array 3. Repeat step 1&2 until done C implementation of algorithm: .

- 19. Computer System Application Software Solve a particular user-level problem May need system software for execution Resides on computer’s hard disk or removable storage media Examples: MATLAB, PSIM… apps: UBER, Amazon… System Software A collection of programs that helps the users to create, analyze and run their programs Typical operations: •Managing, linking, running application programs •File management in secondary storage devices •Running standard applications such as word processor, internet browser •Managing I/O units Examples: Compilers and assemblers , Linkers and loaders, Editors and debuggers 19 A software or a program consists of a set of instructions required to solve a specific problem

- 20. Computer System 20 • Executed directly by hardware • Instructions consists of binary code: 1’s and 0’s Machine Language • Low-level symbolic version • One to one correspondence with machine language • Pseudo instructions are more readable and easy to use Assembly Language • C, C++, Java • Most readable and closer to human languages High-Level Language Programming Language

- 21. Computer System Application Software Algorithm Programming Language Operating System Compiler Instruction set architecture Microarchitecture Register Transfer Level Gate level (logic) Circuits Devices Physics/Technology 21 Computer Architecture Mac OS X, Windows, Linux Handles low-level hardware management RISC-V Instruction Set Instructions that machine executes C Compiler Transform programs into assembly int a = b + c; add r1, r2, r3 How data flows through system Boolean logic gates and functions

- 22. Computer System OS is a collection of routines that is used to control sharing of various computer resources as they execute application programs. Kernel: contains low-level routines for resource management Shell: provides an interface for users to interact with the computer hardware through the kernel 22 Operating System: Provides interface between computer hardware and users

- 23. Computer System OS may have different goals based intended use of computer Classical multi-programming systems Modern time-sharing systems Real-time systems Mobile (phone) systems 23 Operating System: Tasks performed by OS: Assigning memory and disk space to program and data files Moving data between I/O devices, memory and disk units Handling I/O operations, with parallel operations where possible. Handling multiple user programs that are running at the same time.

- 24. Computer System Assembler Translates an assembly language program to machine language. Compiler Translate a high-level language programs to assembly/machine language. 24 Cross-assembler or Cross-compiler: Compiler or assembler when run on another machine instead of native machine for which target code is being generated

- 25. Computer System Application Software Algorithm Programming Language Operating System Compiler Instruction set architecture Microarchitecture Register Transfer Level Gate level (logic) Circuits Devices Physics/Technology 25 Computer Architecture Combining devices to do useful work Silicon process technology Transistors and wires

- 26. Computer Architecture 26 Digital logic: • Logic to process data • State to store data • Interconnect to move data Computer architecture • Processors for computation • Memories for storage • Networks for communication The architecture is the programmer’s view of a computer. It is defined by the instruction set (language), and operand locations (registers and memory). Many different architectures exist, such as IA-32, MIPS, SPARC, and PowerPC Basic Building Blocks

- 27. Computer Architecture 27 von-Neumann Architecture Harvard Architecture Separate memory for program and data Instruction and data are accessed in parallel Instructions and data are stored in same memory Flexible and easy to implement Processor-memory bus acts as the bottleneck. All instructions and data are moved back and forth through the pipe.

- 29. Computer Architecture Processor/Central Processing Unit (CPU) ALU: Arithmetic logic unit contains registers for temporary storage of data It contains circuitry to carry out logic and arithmetic operations Control Unit: generates sequence of control signals to carry out all operations Memory Unit: Memory considered as a linear array of storage locations (bytes or words) each with unique address. 29

- 30. Computer Architecture Input Unit Used to feed data to the computer system from the external environment. Data are transferred to the processor/memory after appropriate encoding Common input devices: – Keyboard – Mouse – Joystick – Camera Output Unit Used to send the result of some computation to the outside world. Common output devices: – LCD/LED screen – Printer – Speaker / Buzzer – Projection system 30

- 31. Computer Architecture BUS Bus refers to a group of lines that serves as a connecting path for several devices. Advantages of multi-bus architecture: Allows multiple data transfer micro-operations to be executed in the same clock cycle overall faster instruction execution multiple shorter buses: Smaller parasitic capacitance, and hence smaller delay 31 One data transfer allowed in 1 clock cycle Parallelism in data transfer is allowed

- 32. Computer Architecture BUS Single bus Architecture inside the processor: 32

- 33. Computer Architecture Memory Unit Two types: Primary or Main memory: stores the active instructions and data for program being executed on processor. Processor only has direct access to primary memory Secondary memory: used as a backup and stores all active and inactive programs and data, typically as files. Memory system hierarchy: L1 cache, L2 cache, L3 cache, primary memory, secondary memory 33 Special-purpose registers: MAR, MDR, PC, IR

- 34. Computer Architecture Interfacing with Primary Memory Memory Address Register (MAR): Holds the address of the memory location to be accessed. Memory Data Register (MDR): Holds the data that is being written into memory or will receive the data being read out from memory. 34 Special-purpose registers: MAR, MDR, PC, IR Read/write command To read data from memory a) Load the memory address into MAR. b) Issue the control signal READ. c) The data read from the memory is stored into MDR. To write data into memory a) Load the memory address into MAR. b) Load the data to be written into MDR. c) Issue the control signal WRITE.

- 35. Computer Architecture Keeping Track of Instructions Program Counter (PC): Holds memory address of next instruction to be executed. Automatically incremented to point to next instruction when instruction is executed Instruction Register (IR): Temporarily holds an instruction that has been fetched from memory. Need to be decoded to find out instruction type. Contains information data location 35 Special-purpose registers: MAR, MDR, PC, IR Memory address 1000 1001 ADD R1, R2 1002 ADD R1, 04 1003 ADD R2, 04 Need of automatic Counter to go from ML 1001 to 1002 Program Counter Need to store fetched instruction from next ML 1002 Instruction Register PC 1002 PC 1003 IR ADD R1, 04 IR ADD R2, 04 ML Opcode/ Mnemonics Operands 1001 ADD R1, R2

- 36. Instruction Execution Steps in instruction execution: 1. Instruction Fetch (IF) 2. Instruction Decode (ID) 3. ALU operation (EX) 4. Memory Access (MEM) 5. Write Back result to register file (WB) Execution speed is increased by overlapping in a pipeline architecture. 36 In clock cycle 4, instruction 4 is trying IF, while instruction 1 is trying MEM. – In von-Neumann architecture, one of these two operations will have to wait resulting in pipeline slowdown. – In Harvard architecture, both operations can go on without speed penalty

- 37. Instruction Execution Process of instruction execution : ADD R1, LOCA Add the contents of memory location A (LOCA) to the contents of register R1. R1 ⃪ R1 + Mem[LOCA] Steps being carried out are called micro-operations MAR ⃪ PC MDR ⃪ Mem[MAR] IR ⃪ MDR PC ⃪ PC + 4 MAR ⃪ IR[Operand] MDR ⃪ Mem[MAR] R1 ⃪ R1 + MDR 37 Register Content PC 1000 MAR 1000 MDR ADD R1, LCOA IR ADD R1, LCOA PC PC+4=? 1000+4 MAR LCOA=5000 MDR 75 R1 R1+MDR=? 50+75=125 Address Content 1000 ADD R1, LCOA 1004 - 5000 75 LCOA

- 39. Number system 39 Decimal • base 10>> 0,1,2,…,9 Binary • base 2>> 0,1 Hexadecimal • base 16>> 0,1,2,…,9,A,B,…,F

- 40. Number system 40 Decimal • base 10>> 0,1,2,…,9 Binary • base 2>> 0,1 Hexadecimal • base 16>> 0,1,2,…,9,A,B,…,F Bit Single binary digit (0 or 1) Nibble Collection of 4 bits Byte Collection 8 bits Word 32 or 64 bits (machine dependent)

- 41. Number system 41 Decimal • base 10>> 0,1,2,…,9 Binary • base 2>> 0,1 Hexadecimal • base 16>> 0,1,2,…,9,A,B,…,F

- 42. 42

- 43. Number System 43 . Binary to Decimal Ans. 10101002 Decimal to Binary Convert 8410 to binary Ans. 2210 Convert 101102 to decimal

- 44. Number System 44 . Hexadecimal to Binary Ans. 74910 Ans. 0010111011012 each hexadecimal digit directly corresponds to four binary digits Convert hexadecimal number 2ED16 to binary and decimal 216 00102, E16 11102 and D16 11012 Hexadecimal to Decimal

- 45. Number System 45 . Binary to Hexadecimal Ans. 7A16 Start reading from the right. The four least significant bits are 10102 A16. The next bits are 1112 716 Convert 11110102 to hexadecimal Decimal to Hexadecimal Convert 33310 to hexadecimal and binary 1010011012 14D16

- 46. Number System 46 Binary Addition 01112 + 01012 =11002 Binary addition with overflow 11012 + 01012 This result overflows the range of a 4-bit binary number. If it must be stored as four bits, the most significant bit is discarded, leaving the incorrect result of 00102

- 47. Number System 47 Two’s Complement Numbers Start with 210 >> 00102. To get -210, invert the bits and add 1 Inverting 00102 produces 11012. 11012+1 = 11102. So -210 is 11102 Represent -210 as a 4-bit two’s complement number Decimal value of the two’s complement number 10012 10012 has a leading 1, so it must be negative. Invert the bits and add 1 Inverting 10012 = 01102. 01102+1 = 01112. = -710

- 48. Number System 48 Two’s Complement Numbers Find two’s complement of -210 i.e 11102 11102+0001 = 11112. invert the bits and add 1 Now find the decimal value of 11112=-110 As MSB is 1, number is negative -210 + 110

- 49. Instruction set architecture For example, Intel and AMD both implement x86 ISA using different microarchitectures 49 Instruction set architecture: is the structure of a computer that a machine language programmer must understand to write a correct (timing independent) program for that machine.” Microarchitecture concepts deal with how the ISA is implemented. Concepts such as instruction pipelining, branch prediction, out of order execution are all employed to achieve an efficient (fast and power-effective(?)) realization of the ISA

- 50. Instruction set architecture By early 1960’s, IBM had several incompatible lines of computers! Why? – Defense : 701 – Scientific : 704, 709, 7090, 7094 – Business : 702, 705, 7080 – Mid-Sized Business : 1400 – Decimal Architectures : 7070, 7072, 7074 Each system had its own: – Implementation and potentially even technology – Instruction set – I/O system and secondary storage – Assemblers, compilers, libraries, etc – Application niche 50 IBM 360 was the first line of machines to separate ISA from microarchitecture Enabled same software to run on different current and future microarchitectures Reduced impact of modifying the microarchitecture enabling rapid innovation in hardware

- 51. ISA Serves as an interface between software and hardware. Typically consists of information regarding the programmer’s view of the architecture (i.e. the registers, address and data buses, etc.). Also consists of the instruction set. 51

- 52. Instruction Set Architecture ISA: the portion of the computer visible to the programmer or compiler writer The words in a computer’s language are called instructions. The computer’s vocabulary is called the instruction set All programs running on a computer use the same instruction set. Even complex software applications, such as word processing and spreadsheet applications, are eventually compiled into a series of simple instructions such as add, subtract, and jump. Computer instructions indicate both the operation to perform and the operands to use. The operands may come from memory, from registers, or from the instruction itself 52

- 53. Instruction Set Design Issues Number of explicit operands: 0, 1, 2 or 3. Location of the operands: Registers, accumulator, memory, accumulator. Specification of operand locations: Addressing modes: register, immediate, indirect, relative, etc. Sizes of operands supported: Byte (8-bits), Half-word (16-bits), Word (32-bits), Double (64-bits), etc. Supported operations: ADD, SUB, MUL, AND, OR, CMP, MOVE, JMP, etc. 53

- 54. ISA Evolution/ Classification of ISA 1. Accumulator based: 1960’s (EDSAC, IBM 1130) 2. Stack based: 1960-70 (Burroughs 5000) 3. Memory-Memory based: 1970-80 (IBM 360) 4. Register-Memory based: 1970-present (Intel x86) 5. Register-Register based: 1960-present (MIPS, CDC 6600, SPARC) 54 An accumulator is a type of register for short-term, intermediate storage of arithmetic and logic data in a computer's central processing unit (CPU)

- 55. Classification of ISA 55 1. Accumulator based: 1960’s (EDSAC, IBM 1130)

- 56. Classification of ISA 56 2. Stack based: 1960-70 (Burroughs 5000)

- 57. Classification of ISA 57 3. Memory-Memory based: 1970-80 (IBM 360) ALU Operands From Memory Result stored to Memory ADD Z, X, Y

- 58. Classification of ISA 58 4. Register-Memory based: 1970-present (Intel x86)

- 59. Classification of ISA 59 5. Register-Register based: 1960-present (MIPS, CDC 6600, SPARC)

- 60. Classification of ISA: Summary 60 Code sequence for C = A + B for four classes of instruction sets Book1 Pg:527

- 64. Classification of ISA 64 Typical combinations of memory operands and total operands per typical ALU instruction with examples of computers

- 65. Classification of ISA Critical thinking?? Q: What is the significance/advantage of using General-purpose register (GPR) computers ISA in load store architecture over other formats of ISA (e.g. accumulator based ISA, stack based ISA, memory based ISA) Q Compare(Write advantage and disadvantages of) Register-Register ISA, Register-Memory ISA, Memory-Memory ISA 65

- 66. Memory Addressing Two different conventions for ordering the bytes Little Endian byte order puts the byte whose address is “x . . . x000” at the least-significant position in the double word (the little end). The bytes are numbered: Big Endian byte order puts the byte whose address is “x . . . x000” at the most significant position in the double word (the big end). The bytes are numbered: 66 Data: 23456789

- 67. Addressing Modes How architectures specify the address of an object they will access? Addressing modes specify the mechanism by which operand can be located Operand can be a constant, register, memory location When a memory location is used, the actual memory address specified by the addressing mode is called the effective address Not all processors support all addressing modes. Features: have ability to significantly reduce instruction counts; may add to complexity of building a computer may increase the average clock cycles per instruction (CPI) of computers that implement those modes. 67 Addressing Modes

- 68. Addressing Modes 1. Immediate Addressing Mode Operand is part of the instruction itself Fast but limited range (because a limited number of bits are provided to specify the immediate data Examples: – ADD #25 // ACC = ACC + 25 – ADDI R1,R2,42 // R1 = R2 + 42 68

- 69. Addressing Modes 2. Direct Addressing Mode Instruction contains a field that holds the memory address of the operand. Single memory access is required to access the operand. – No additional calculations required to determine the operand address. – Limited address space (as number of bits is limited, say, 16 bits). Examples: ADD R1,20A6H // R1 = R1 + Mem[20A6] 69

- 70. Addressing Modes 3. Indirect Addressing Mode The instruction contains a field that holds the memory address, which in turn holds the memory address of the operand. •Two memory accesses are required to get the operand value. • Slower but can access large address space. •Not limited by the number of bits in operand address like direct addressing. Examples: ADD R1,(20A6H) // R1 = R1 + (Mem[20A6]) 70

- 71. Addressing Modes 4. Register Addressing Mode The operand is held in a register, and the instruction specifies the register number. •Very few number of bits needed, as the number of registers is limited. •Faster execution, since no memory access is required for getting the operand. •Modern load-store architectures support large number of registers. Examples: ADD R1,R2,R3 // R1 = R2 + R3 MOV R2,R5 // R2 = R5 71

- 72. Addressing Modes 4. Register Indirect Addressing Mode The instruction specifies a register, and the register holds the memory address where the operand is stored. – Can access large address space. – fewer memory access as compared to indirect addressing. Examples: ADD R1,(R5) // PC = R1 + Mem[R5] 72

- 73. Addressing Modes 4. Relative Addressing Mode (PC Relative) The instruction specifies an offset of displacement, which is added to the program counter (PC) to get the effective address of the operand. – Since the number of bits to specify the offset is limited, the range of relative addressing is also limited. – If a 12-bit offset is specified, it can have values ranging from -2048 to +2047. 73

- 74. Addressing Modes 6. Indexed Addressing Mode The instruction specifies an offset of displacement, which is added to the index register to get the effective address of the operand. – Either a special-purpose register, or a general- purpose register, is used as index register in this addressing mode. – Can be used to sequentially access the elements of an array. – Offset gives the starting address of the array, and the index register value specifies the array element to be used Examples: LOAD R1,1050(R3) // R1 = Mem[1050+R3] 74

- 75. Addressing Modes 7. Stack Addressing Mode Operand is implicitly on top of the stack. Many processors have a special register called the stack pointer (SP) that keeps track of the stack-top in memory. – PUSH, POP, CALL, RET instructions automatically modify SP. Examples: ADD PUSH X POP X 8. Autoincrement and Autodecrement Addressing Mode The register holding the operand address is automatically incremented or decremented after accessing the operand (like a++ and a-- in C). 75

- 76. 76 array Mem as the name for main memory and the array Regs for registers. Thus, Mem[Regs[R1]] refers to the contents of the memory location whose address is given by the contents of register 1 (R1). In autoincrement/-decrement and scaled addressing modes, the variable d designates the size of the data item being accessed (i.e., whether the instruction is accessing 1, 2, 4, or 8 bytes). These addressing modes are only useful when the elements being accessed are adjacent in memory.

- 77. 77

- 78. RISC and CISC ISA Broad classification of ISA: 1. RISC (Reduced Instruction Set Computer) 2. CISC (Complex Instruction Set Computer) 78

- 79. RISC and CISC ISA Broad classification of ISA: 1. RISC (Reduced Instruction Set Computer) 2. CISC (Complex Instruction Set Computer) 79

- 80. 80 S.No 8051 ARM 1. 8 bit for standard core bus width is present in 8051 micro- controller. Mostly 32 bit bus width is present in ARM micro-controller and also 64-bit is available. 2. Its speed is 12 clock cycles per machine cycle. Its speed is 1 clock cycle per machine cycle. 3. UART, USART, I2C, SPI, communication protocols are used. UART, USART, Ethernet, I2S, DSP, SPI, CAN, LIN, I2C communication protocols are used. 4. Flash, ROM, SRAM memory is used in 8051 micro- controller. Flash, EEPROM, SDRAM memory is used in ARM micro- controller. 5. It is based on CISC Instruction set Architecture. It is based on RISC Instruction Set Architecture. 6. 8051 micro-controller is a Harvard-based architecture, but it allows us to connect external memory and simulate von Neumann’s architecture. PIC micro-controller is based on Harvard architecture. 7. Power consumption of 8051 micro-controller is average. Power consumption of ARM micro-controller is low. 8. Its families include 8051 variants. Its families include ARMv4, 5, 6, 7 and cortex series. 9. Its manufacturers are Atmel, NXP, Silicon Labs, Dallas, Cyprus, Infineon, etc. Its manufacturers are Nvidia, Qualcomm, Apple, Samsung Electronics, and TI etc. 10. 8051 micro-controller costs very low as compared to features provided. ARM micro-controller costs low as compared to features provided. 11. Popular micro-controllers include AT89C51, P89v51, etc. Popular micro-controllers include ARM Cortex-M0 to ARM Cortex-M7, etc.

- 81. Measuring CPU Performance Clock rate or frequency f: Most processors execute instructions in a synchronous manner using a clock that runs at a constant clock rate or frequency f. f depends on :Implementation technology and CPU organization Clock cycle time C C = 1 / f Cycles Per Instruction(CPI) A single machine instruction may take one or more CPU cycles to complete. Average CPI of a program: Average CPI of all instruction executed in the program on a given processor 81 Micro-operation: •It is an elementary hardware operation that can be carried out in one clock cycle •A machine instruction consists of a number of elementary micro- operations that vary in number and complexity depending on the instruction and the CPU organization used •Eg: Register transfer operation, arithmetic and logic operations, etc. .

- 82. Measuring CPU Performance Execution Time: XT = IC x CPI x C Performance Perf =1/XT PerfA = 1 / XTA PerfB = 1 / XTB Speedup = PerfA / PerfB = XTB / XTA 82 The total number of instructions executed or instruction count (IC). The average number of cycles per instruction (CPI). Clock cycle time (C) C = 1 / f where f is clock frequency of machine Comment on: RISC vs CiSC RISC: increases IC, but decreases CPI and clock cycle time and hence the implementations are simple. CISC: decreases IC, but increases CPI and clock cycle time because many instructions are more complex.

- 83. Measuring CPU Performance An example: A program is run on three different machines A, B and C and execution times of 10, 25 and 75 are noted. – A is 2.5 times faster than B – A is 7.5 times faster than C – B is 3.0 times faster than C 83

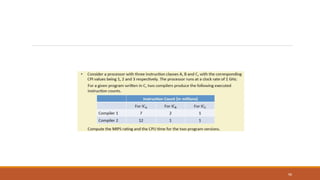

- 93. 93

- 94. 94

- 95. BENCHMARKS Set of standard programs used to comparison is called benchmark. MIPS (Million Instructions Per Second) – Computed as (IC / XT) x 10-6 The MIPS rating is only valid to compare the performance of two or more processors when a) The same program is used b) The same ISA is used c) The same compiler is used identical at the machine code level with the same instruction count MFLOPS (Million Floating Point Operations Per Second) Simply computes number of floating-point operations executed per second. 95

- 96. 96

- 97. 97

- 98. 98

- 99. 99

- 100. 100

- 101. Benchmarking Different levels of programs used for benchmarking: a) Real applications (SPEC95, SPEC CPU2000 ) b) Kernel benchmarks c) Toy benchmarks d) Synthetic benchmarks 101

- 102. 102

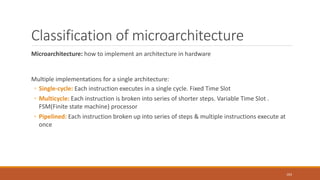

- 103. Classification of microarchitecture Microarchitecture: how to implement an architecture in hardware Multiple implementations for a single architecture: ◦ Single-cycle: Each instruction executes in a single cycle. Fixed Time Slot ◦ Multicycle: Each instruction is broken into series of shorter steps. Variable Time Slot . FSM(Finite state machine) processor ◦ Pipelined: Each instruction broken up into series of steps & multiple instructions execute at once 103

- 105. Processor/Laundry Analogy • Processor – Instructions are “transactions” that execute on a processor – Architecture: defines the hardware/software interface – Microarchitecture: how hardware executes sequence of instructions • Laundry – Cleaning a load of laundry is a “transaction” – Architecture: high-level specification, dirty clothes in, clean clothes out – Microarchitecture: how laundry room actually processes multiple loads 105

- 106. 106

- 107. 107

- 108. Instruction Execution Steps in instruction execution: 1. Instruction Fetch (IF) 2. Instruction Decode (ID) 3. ALU operation (EX) 4. Memory Access (MEM) 5. Write Back result to register file (WB) Execution speed is increased by overlapping in a pipeline architecture. 108 In clock cycle 4, instruction 4 is trying IF, while instruction 1 is trying MEM. – In von-Neumann architecture, one of these two operations will have to wait resulting in pipeline slowdown. – In Harvard architecture, both operations can go on without speed penalty

- 109. 109

- 110. 110

- 111. Processor Functional-Level Model 111 Lets assume: Each instruction as a transaction Executing a transaction involves a sequence of steps

Editor's Notes

- #7: Computers everywhere in some form of processing unit

- #8: Computers everywhere in some form of processing unit embedded computer, a computer that is integrated into another system for the purposes of control and/or monitoring hidden inside his TVs, VCRs, DVD players, remote controls, washing machines, cell phones, air conditioners, game consoles, ovens, toys, and a host of other devices primary difference between an embedded machine and a general-purpose computer is its application. The basic principles of operation and the underlying architectures are fundamentally the same. the embedded computer is normally dedicated to a specific task. embedded computer may or may not have an operating system. An embedded computer may be implemented in a single chip with just a few support components, and its purpose may be as crude as a controller for a garden-watering system. Alternatively, the embedded computer may be a 150-processor, distributed parallel machine responsible for all the flight and control systems of a commercial jet.

- #9: Source:https://www.daenotes.com/electronics/devices-circuits/integrated-circuits-ic Solid Logic Technology (SLT), technology before monolithic IC. was IBM's method for hybrid packaging of electronic circuitry introduced in 1964 with the IBM System/360 series of computers and related machines.[1] IBM chose to design custom hybrid circuits using discrete, flip chip-mounted, glass-encapsulated transistors and diodes, with silk-screened resistors on a ceramic substrate, forming an SLT module. The circuits were either encapsulated in plastic or covered with a metal lid.

- #10: At the lowest level, there are programs that are run by the processor when the computer first powers up. These programs initialize the other hardware subsystems to a known state and configure the computer for cor The bootloader is located in the firmware. The bootloader is a special program run by the processor that reads the operating system from disk (or nonvolatile memory or network interface) and places it in memory so that the processor may then run it. The bootloader is present in desktop computers and workstations, and may be present in some embedded computers.rect operation. This software, because it is permanently stored in the computer’s memory, is known as firmware Above the firmware, the operating system controls the operation of the computer. It organizes the use of memory and controls devices such as the keyboard, mouse, screen, disk drives, and so on. It is also the software that often provides an interface to the user, enabling her to run application programs and access her files on disk. The operating system typically provides a set of software tools for application programs, providing a mechanism by which they too can access the screen, disk drives, and so on. Not all embedded systems use or even need an operating system. At the highest level, the application software constitutes the programs that provide the functionality of the computer. Everything below the application is considered system software . For embedded computers, the boundary between application and system software is often blurred.

- #14: What this means is that computers are projected to reach their limits because transistors will be unable to operate within smaller circuits at increasingly higher temperatures. This is due to the fact that cooling the transistors will require more energy than the energy that passes through the transistor itself.

- #18: The field of computer architecture has recently evolved through the single-core era and multi-core era and is now in the accelerator era making it an exciting time to study computer architecture

- #19: Using the power of abstraction, the grandmother or a even a kid can surf the Web without any regard for the quantum vibrations of electrons or the organization of the memory in her computer. Microarchitecture links the logic and architecture levels of abstraction. The architecture level of abstraction describes a computer from the programmer’s perspective For example, the Intel IA-32 architecture used by microprocessors in most personal computers (PCs) is defined by a set of instructions and registers (memory for temporarily storing variables) that the programmer is allowed to use. Microarchitecture involves combining logic elements to execute the instructions defined by the architecture. A particular architecture can be implemented by one of many different microarchitectures with different price/performance/power trade-offs. Intel Core 2 Duo, the Intel 80486, and the AMD Athlon all implement the IA-32 architecture with different microarchitectures the operating system handles lowlevel details such as accessing a hard drive or managing memory. Finally, the application software uses these facilities provided by the operating system to solve a problem for the user.

- #22: Microarchitecture links the logic and architecture levels of abstraction. The architecture level of abstraction describes a computer from the programmer’s perspective For example, the Intel IA-32 architecture used by microprocessors in most personal computers (PCs) is defined by a set of instructions and registers (memory for temporarily storing variables) that the programmer is allowed to use. Microarchitecture involves combining logic elements to execute the instructions defined by the architecture. A particular architecture can be implemented by one of many different microarchitectures with different price/performance/power trade-offs. Intel Core 2 Duo, the Intel 80486, and the AMD Athlon all implement the IA-32 architecture with different microarchitectures the operating system handles lowlevel details such as accessing a hard drive or managing memory. Finally, the application software uses these facilities provided by the operating system to solve a problem for the user.

- #24: Real-Jme systems • Several applicaJons are running with specific deadlines. • Deadlines can be either hard or sob. • Interrupt-driven operaJon – processor interrupted when a task arrives. • Examples: missile control system, industrial manufacturing plant, paJent health monitoring and control system, automoJve control system, etc. – Mobile (phone) systems • Here user responsiveness is the most important. • SomeJmes a program that makes the system slow or hogs too much memory may be forcibly stopped. Classical mulJ-programming systems • Several user programs loaded in memory. • Switch to another program when one program gets blocked due to I/O. • ObjecJve is to maximize resource uJlizaJon. – Modern Jme-sharing systems • Widely used because every user can now afford to have a separate terminal. • Processor Jme shared among a number of interacJve users. • ObjecJve is to reduce the user response Jme.

- #26: Microarchitecture links the logic and architecture levels of abstraction. The architecture level of abstraction describes a computer from the programmer’s perspective For example, the Intel IA-32 architecture used by microprocessors in most personal computers (PCs) is defined by a set of instructions and registers (memory for temporarily storing variables) that the programmer is allowed to use. Microarchitecture involves combining logic elements to execute the instructions defined by the architecture. A particular architecture can be implemented by one of many different microarchitectures with different price/performance/power trade-offs. Intel Core 2 Duo, the Intel 80486, and the AMD Athlon all implement the IA-32 architecture with different microarchitectures the operating system handles lowlevel details such as accessing a hard drive or managing memory. Finally, the application software uses these facilities provided by the operating system to solve a problem for the user.

- #29: Computer architecture is the process of building computing systems to meet given application requirements within physical technology constraints

- #32: Allows mulJple data transfer micro-operaJons to be executed in the same clock cycle.

- #36: To read data from memory a) Load the memory address into MAR. b) Issue the control signal READ. c) The data read from the memory is stored into MDR. • To write data into memory a) Load the memory address into MAR. b) Load the data to be wrioen into MDR. c) Issue the control signal WRITE.

- #38: PC incremented by 4 for 32 bit machine PC=PC+4 for 64 bit m/c

- #40: Writing long binary numbers becomes tedious and prone to error

- #41: Writing long binary numbers becomes tedious and prone to error Range: N-digit decimal number represents one of 10N possibilities: 0, 1,2, 3, ..., 10N-1. Eg : three-digit decimal number represents one of 1000 possibilities in the range of 0 to 999

- #42: Writing long binary numbers becomes tedious and prone to error

![Instruction Execution

Process of instruction execution :

ADD R1, LOCA

Add the contents of memory location A (LOCA) to the

contents of register R1.

R1 ⃪ R1 + Mem[LOCA]

Steps being carried out are called

micro-operations

MAR ⃪ PC

MDR ⃪ Mem[MAR]

IR ⃪ MDR

PC ⃪ PC + 4

MAR ⃪ IR[Operand]

MDR ⃪ Mem[MAR]

R1 ⃪ R1 + MDR

37

Register Content

PC 1000

MAR 1000

MDR ADD R1, LCOA

IR ADD R1, LCOA

PC PC+4=?

1000+4

MAR LCOA=5000

MDR 75

R1 R1+MDR=?

50+75=125

Address Content

1000 ADD R1, LCOA

1004 -

5000 75

LCOA](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-37-320.jpg)

![Addressing Modes

2. Direct Addressing Mode

Instruction contains a field that holds the memory

address of the operand.

Single memory access is required to access the

operand.

– No additional calculations required to determine

the operand address.

– Limited address space (as number of bits is

limited, say, 16 bits).

Examples:

ADD R1,20A6H // R1 = R1 + Mem[20A6]

69](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-69-320.jpg)

![Addressing Modes

3. Indirect Addressing Mode

The instruction contains a field that holds the

memory address, which in turn holds the memory

address of the operand.

•Two memory accesses are required to get the

operand value.

• Slower but can access large address space.

•Not limited by the number of bits in operand

address like direct addressing.

Examples:

ADD R1,(20A6H) // R1 = R1 + (Mem[20A6])

70](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-70-320.jpg)

![Addressing Modes

4. Register Indirect Addressing Mode

The instruction specifies a register, and the register

holds the memory address where the operand is

stored.

– Can access large address space.

– fewer memory access as compared to indirect

addressing.

Examples:

ADD R1,(R5) // PC = R1 + Mem[R5]

72](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-72-320.jpg)

![Addressing Modes

6. Indexed Addressing Mode

The instruction specifies an offset of displacement,

which is added to the index register to get the

effective address of the operand.

– Either a special-purpose register, or a general-

purpose register, is used as index register in this

addressing mode.

– Can be used to sequentially access the elements

of an array.

– Offset gives the starting address of the array, and

the index register value specifies the array element

to be used

Examples:

LOAD R1,1050(R3) // R1 = Mem[1050+R3]

74](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-74-320.jpg)

![76

array Mem as the name for main memory and the array Regs for registers. Thus, Mem[Regs[R1]] refers to the

contents of the memory location whose address is given by the contents of register 1 (R1).

In autoincrement/-decrement and scaled addressing modes, the variable d designates the size of the data item

being accessed (i.e., whether the instruction is accessing 1, 2, 4, or 8 bytes). These addressing modes are only

useful when the elements being accessed are adjacent in memory.](https://image.slidesharecdn.com/unit1new1-240630032926-4ad25b17/85/microprocessor-and-microcontroller-material-76-320.jpg)

![Eee iv-microcontrollers [10 es42]-notes](https://cdn.slidesharecdn.com/ss_thumbnails/eee-iv-microcontrollers10es42-notes-190903091207-thumbnail.jpg?width=560&fit=bounds)