Optimizing shared caches in chip multiprocessors

Download as PPTX, PDF1 like202 views

Chip multiprocessors, which place multiple processors on a single chip, have become common in modern processors. There are various approaches to managing caches in chip multiprocessors, including private caches for each processor core or shared caches that all cores can access. The optimal approach balances factors like minimizing traffic between cores, avoiding duplication of cached data, and reducing latency.

1 of 21

Download to read offline

Ad

Recommended

Microkernel-based operating system development

Microkernel-based operating system developmentSenko Rašić The document discusses microkernel-based operating system development. It describes how a microkernel has minimal functionality and moves drivers and services to user-level processes that communicate through inter-process communication calls. This can impact performance. Mainstream systems now take a hybrid approach. The document then describes the L4 microkernel and its implementation, Hasenpfeffer, which maximizes reuse of open source components. It lists components and features of the Hasenpfeffer system, including programming languages, drivers, and tools for development.

Microkernel Evolution

Microkernel EvolutionNational Cheng Kung University This presentation covers 3 Generations of Microkernels: Mach, L4, seL4/Fiasco.OC/NOVA.

In addition, the real use cases are included.

Red Hat System Administration

Red Hat System AdministrationRafi Rahimov This document provides an overview of topics covered in a Red Hat System Administration training course, including:

1) Managing files graphically with Nautilus and getting help in both graphical and textual environments.

2) Managing physical storage by creating and formatting partitions, and managing logical volumes using LVM concepts.

3) Monitoring system resources such as processes, disk usage, and software packages.

4) Configuring networking and managing users, groups, and permissions.

olibc: Another C Library optimized for Embedded Linux

olibc: Another C Library optimized for Embedded LinuxNational Cheng Kung University http://olibc.so/

– Review C library characteristics

– Toolchain optimizations

– Build configurable runtime

– Performance evaluation

Making Linux do Hard Real-time

Making Linux do Hard Real-timeNational Cheng Kung University This document discusses making Linux capable of hard real-time performance. It begins by defining hard and soft real-time systems and explaining that real-time does not necessarily mean fast but rather determinism. It then covers general concepts around real-time performance in Linux like preemption, interrupts, context switching, and scheduling. Specific features in Linux like RT-Preempt, priority inheritance, and threaded interrupts that improve real-time capabilities are also summarized.

seL4 intro

seL4 intromicrokerneldude Introduction to principles, concepts and mechanisms of the seL4 microkernel. Overview of the kernel API and programming examples

A Reimplementation of NetBSD Based on a Microkernel by Andrew S. Tanenbaum

A Reimplementation of NetBSD Based on a Microkernel by Andrew S. Tanenbaumeurobsdcon Minix 3 is a reimplementation of NetBSD based on a microkernel architecture. It aims to build a highly reliable operating system through isolation of components, running drivers and servers as user-mode processes, and making the system self-healing. The presentation outlines the architecture and goals of Minix 3, and encourages participation from the audience to help further develop and expand the system.

Running Applications on the NetBSD Rump Kernel by Justin Cormack

Running Applications on the NetBSD Rump Kernel by Justin Cormack eurobsdcon Abstract

The NetBSD rump kernel has been developed for some years now, allowing NetBSD kernel drivers to be used unmodified in many environments, for example as userspace code. However it is only since last year that it has become possible to easily run unmodified applications on the rump kernel, initially with the rump kernel on Xen port, and then with the rumprun tools to run them in userspace on Linux, FreeBSD and NetBSD. This talk will look at how this is achieved, and look at use cases, including kernel driver development, and lightweight process virtualization.

Speaker bio

Justin Cormack has been a Unix user, developer and sysadmin since the early 1990s. He is based in London and works on open source cloud applications, Lua, and the NetBSD rump kernel project. He has been a NetBSD developer since early 2014.

Introduction to Microkernels

Introduction to MicrokernelsVasily Sartakov This document provides an introduction to microkernel-based operating systems using the Fiasco.OC microkernel as an example. It outlines the key concepts of microkernels, including using a minimal kernel to provide mechanisms like threads and address spaces while implementing operating system services like filesystems and networking in user-level servers. It describes the objects and capabilities model of the Fiasco.OC microkernel and how it implements threads and inter-process communication. It also discusses how the L4 runtime environment builds further services on top of the microkernel to provide a full operating system environment.

Plan 9: Not (Only) A Better UNIX

Plan 9: Not (Only) A Better UNIXNational Cheng Kung University Plan 9 was an operating system designed in the 1980s by Bell Labs as a distributed successor to Unix. It treated all system resources, including files, devices, processes and network connections, as files that could be accessed through a single universal file system interface. Plan 9 assumed a network of reliable file servers and CPU servers with personal workstations accessing aggregated remote resources through a high-speed network. It aimed to "build a UNIX out of little systems" rather than integrating separate systems.

From L3 to seL4: What have we learnt in 20 years of L4 microkernels

From L3 to seL4: What have we learnt in 20 years of L4 microkernelsmicrokerneldude The document summarizes learnings from 20 years of L4 microkernel development. It discusses how early L4 designs focused on performance through techniques like lazy scheduling and direct process switching, but modern kernels emphasize principles like minimality and formal verification. Minimality has driven designs to become simpler over time, with policies separated from mechanisms and drivers moved to user-space. While IPC speed remains important, verification shows it need not compromise performance. Capabilities have also proven effective for access control compared to early process hierarchies. Overall, microkernels remain valuable if guided by core principles demonstrated over L4's evolution.

Linux kernel Architecture and Properties

Linux kernel Architecture and PropertiesSaadi Rahman This document discusses the key components and architecture of the Linux kernel. It begins by defining the kernel as the central module of an operating system that loads first and remains in memory, providing essential services. It then describes the major subsystems of Linux, including process management, memory management, virtual file systems, network stacks, and device drivers. It concludes that the modular design of the Linux kernel has supported its growth and success through independent and extensible development of these subsystems.

μ-Kernel Evolution

μ-Kernel EvolutionSergio Shevchenko Mach was an early microkernel-based operating system from the 1980s that served as the basis for several later systems. It employed asynchronous inter-process communication (IPC) which led to significant performance penalties compared to monolithic kernels. The L3 and L4 microkernels from the 1990s improved IPC performance by an order of magnitude through techniques like synchronous IPC and architecture-specific optimizations. This helped validate that microkernels could achieve adequate performance. L4Linux brought the Linux kernel to run as a user process on top of L4 microkernels like Fiasco.OC. It required paravirtualizing portions of Linux to interface with the microkernel but typically incurred only 5-10% performance penalties compared to native

Architecture Of The Linux Kernel

Architecture Of The Linux Kernelguest547d74 The document discusses the architecture of the Linux kernel. It describes the user space and kernel space components. In user space are the user applications, glibc library, and each process's virtual address space. In kernel space are the system call interface, architecture-independent kernel code, and architecture-dependent code. It then covers several kernel subsystems like process management, memory management, virtual file system, network stack, and device drivers.

Parallel Computing - Lec 3

Parallel Computing - Lec 3Shah Zaib This document discusses parallel hardware and techniques for exploiting parallelism. It covers instruction level parallelism techniques like pipelining and simultaneous multithreading. It also discusses parallel architectures like SIMD, vector processors, shared memory systems, distributed memory systems, and interconnection networks. Cache coherence protocols like MESI are presented to ensure data consistency across cores that share memory. Examples of multicore CPUs and supercomputers are provided to illustrate these concepts.

L4 Microkernel :: Design Overview

L4 Microkernel :: Design OverviewNational Cheng Kung University (1) Myths of Microkernel

(2) Characteristics of 2nd generation microkernel

(3) Toward 3rd generation microkernel

Pacemaker+DRBD

Pacemaker+DRBDDan Frincu The document provides a history of high availability clustering technologies, including Heartbeat, OpenAIS/Corosync, Pacemaker, and DRBD. It discusses how these projects have evolved over time, with Heartbeat focusing only on messaging, OpenAIS/Corosync providing improved scalability, Pacemaker controlling resources and supporting multiple stacks, and DRBD enabling shared storage across nodes. It also outlines future directions like Pacemaker Cloud for cloud deployments and stretch clusters for multi-site scalability.

[TALK] Exokernel vs. Microkernel![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

[TALK] Exokernel vs. MicrokernelHawx Chen http://hawxchen.blogspot.tw/2013/08/talk-exokernel-vs-microkernel.html

I presented this slide at COSCUP 2013 with about 1500 attendees in Taiwan.

I focus on introduction for Exokernel's design and comparison between other kernels, like Microkernel.

Hints for L4 Microkernel

Hints for L4 MicrokernelNational Cheng Kung University Introduce L4 microkernel principles and concepts and Understand the real world usage for microkernels

Embedded Hypervisor for ARM

Embedded Hypervisor for ARMNational Cheng Kung University Agenda:

(1) Virtualization from The Past

(2) Hypervisor Design

(3) Embedded Hypervisors for ARM

(4) Toward ARM Cortex-A15

Multicore Processors

Multicore ProcessorsSmruti Sarangi 1) Design and Implementation of Multicore Processors

2) Coherence and Consistency

3) Power and Temperature

4) Interconnects

5) Multicore Caches

6) Security

7) Real world examples

Implement Runtime Environments for HSA using LLVM

Implement Runtime Environments for HSA using LLVMNational Cheng Kung University * Transition to heterogeneous

- mobile phone to data centre

* LLVM and HSA

* HSA driven computing environment

Ubuntu

UbuntuJacquiline Tabelin The document provides information about the Ubuntu operating system. It discusses Ubuntu's history as a fork of Debian Linux that was created to be more user-friendly. It was founded by Mark Shuttleworth in 2004. The document also covers Ubuntu's design principles, use of the Linux kernel for processes, memory management, file systems, security features, and graphical user interface.

[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)npinto This document summarizes an MIT lecture on GPU cluster programming using MPI. It provides administrative details such as homework due dates and project information. It also announces various donations of computing resources for the class, including Amazon AWS credits and a Tesla graphics card for the best project. The lecture outline covers the problem of computations too large for a single CPU, an introduction to MPI, MPI basics, using MPI with CUDA, and other parallel programming approaches.

Massively Parallel Architectures

Massively Parallel ArchitecturesJason Hearne-McGuiness This document discusses massively parallel architectures and processing in memory (PIM) as ways to overcome the memory wall problem. It describes several PIM and cellular architectures including Cyclops, Gilgamesh, Shamrock, picoChip and DIMES. DIMES is an FPGA implementation of a simplified cellular architecture that was used by Jason McGuiness to test programming approaches. The talk concludes with an invitation for questions.

Introduction to multi core

Introduction to multi coremukul bhardwaj This document provides an introduction to multi-core processors. It discusses that a multi-core processor contains two or more processors on a single integrated circuit. This leads to enhanced performance, reduced power consumption, and more efficient simultaneous processing of multiple tasks. However, developing multithreaded applications for multi-core processors can be difficult, time-consuming, and error-prone. Adding more cores also introduces additional overheads and latencies between communicating and non-communicating cores. There are different types of multi-core architectures including symmetric multiprocessing (SMP) and asymmetric multiprocessing (AMP). Effective use of multi-core processors requires considerations around cache coherency, load balancing, interrupt handling, and concurrency management.

Cache coherence ppt

Cache coherence pptArendraSingh2 This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.

Ad

More Related Content

What's hot (15)

Introduction to Microkernels

Introduction to MicrokernelsVasily Sartakov This document provides an introduction to microkernel-based operating systems using the Fiasco.OC microkernel as an example. It outlines the key concepts of microkernels, including using a minimal kernel to provide mechanisms like threads and address spaces while implementing operating system services like filesystems and networking in user-level servers. It describes the objects and capabilities model of the Fiasco.OC microkernel and how it implements threads and inter-process communication. It also discusses how the L4 runtime environment builds further services on top of the microkernel to provide a full operating system environment.

Plan 9: Not (Only) A Better UNIX

Plan 9: Not (Only) A Better UNIXNational Cheng Kung University Plan 9 was an operating system designed in the 1980s by Bell Labs as a distributed successor to Unix. It treated all system resources, including files, devices, processes and network connections, as files that could be accessed through a single universal file system interface. Plan 9 assumed a network of reliable file servers and CPU servers with personal workstations accessing aggregated remote resources through a high-speed network. It aimed to "build a UNIX out of little systems" rather than integrating separate systems.

From L3 to seL4: What have we learnt in 20 years of L4 microkernels

From L3 to seL4: What have we learnt in 20 years of L4 microkernelsmicrokerneldude The document summarizes learnings from 20 years of L4 microkernel development. It discusses how early L4 designs focused on performance through techniques like lazy scheduling and direct process switching, but modern kernels emphasize principles like minimality and formal verification. Minimality has driven designs to become simpler over time, with policies separated from mechanisms and drivers moved to user-space. While IPC speed remains important, verification shows it need not compromise performance. Capabilities have also proven effective for access control compared to early process hierarchies. Overall, microkernels remain valuable if guided by core principles demonstrated over L4's evolution.

Linux kernel Architecture and Properties

Linux kernel Architecture and PropertiesSaadi Rahman This document discusses the key components and architecture of the Linux kernel. It begins by defining the kernel as the central module of an operating system that loads first and remains in memory, providing essential services. It then describes the major subsystems of Linux, including process management, memory management, virtual file systems, network stacks, and device drivers. It concludes that the modular design of the Linux kernel has supported its growth and success through independent and extensible development of these subsystems.

μ-Kernel Evolution

μ-Kernel EvolutionSergio Shevchenko Mach was an early microkernel-based operating system from the 1980s that served as the basis for several later systems. It employed asynchronous inter-process communication (IPC) which led to significant performance penalties compared to monolithic kernels. The L3 and L4 microkernels from the 1990s improved IPC performance by an order of magnitude through techniques like synchronous IPC and architecture-specific optimizations. This helped validate that microkernels could achieve adequate performance. L4Linux brought the Linux kernel to run as a user process on top of L4 microkernels like Fiasco.OC. It required paravirtualizing portions of Linux to interface with the microkernel but typically incurred only 5-10% performance penalties compared to native

Architecture Of The Linux Kernel

Architecture Of The Linux Kernelguest547d74 The document discusses the architecture of the Linux kernel. It describes the user space and kernel space components. In user space are the user applications, glibc library, and each process's virtual address space. In kernel space are the system call interface, architecture-independent kernel code, and architecture-dependent code. It then covers several kernel subsystems like process management, memory management, virtual file system, network stack, and device drivers.

Parallel Computing - Lec 3

Parallel Computing - Lec 3Shah Zaib This document discusses parallel hardware and techniques for exploiting parallelism. It covers instruction level parallelism techniques like pipelining and simultaneous multithreading. It also discusses parallel architectures like SIMD, vector processors, shared memory systems, distributed memory systems, and interconnection networks. Cache coherence protocols like MESI are presented to ensure data consistency across cores that share memory. Examples of multicore CPUs and supercomputers are provided to illustrate these concepts.

L4 Microkernel :: Design Overview

L4 Microkernel :: Design OverviewNational Cheng Kung University (1) Myths of Microkernel

(2) Characteristics of 2nd generation microkernel

(3) Toward 3rd generation microkernel

Pacemaker+DRBD

Pacemaker+DRBDDan Frincu The document provides a history of high availability clustering technologies, including Heartbeat, OpenAIS/Corosync, Pacemaker, and DRBD. It discusses how these projects have evolved over time, with Heartbeat focusing only on messaging, OpenAIS/Corosync providing improved scalability, Pacemaker controlling resources and supporting multiple stacks, and DRBD enabling shared storage across nodes. It also outlines future directions like Pacemaker Cloud for cloud deployments and stretch clusters for multi-site scalability.

[TALK] Exokernel vs. Microkernel![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![[TALK] Exokernel vs. Microkernel](https://cdn.slidesharecdn.com/ss_thumbnails/coscup2013upload-130805093121-phpapp01-thumbnail.jpg?width=560&fit=bounds)

[TALK] Exokernel vs. MicrokernelHawx Chen http://hawxchen.blogspot.tw/2013/08/talk-exokernel-vs-microkernel.html

I presented this slide at COSCUP 2013 with about 1500 attendees in Taiwan.

I focus on introduction for Exokernel's design and comparison between other kernels, like Microkernel.

Hints for L4 Microkernel

Hints for L4 MicrokernelNational Cheng Kung University Introduce L4 microkernel principles and concepts and Understand the real world usage for microkernels

Embedded Hypervisor for ARM

Embedded Hypervisor for ARMNational Cheng Kung University Agenda:

(1) Virtualization from The Past

(2) Hypervisor Design

(3) Embedded Hypervisors for ARM

(4) Toward ARM Cortex-A15

Multicore Processors

Multicore ProcessorsSmruti Sarangi 1) Design and Implementation of Multicore Processors

2) Coherence and Consistency

3) Power and Temperature

4) Interconnects

5) Multicore Caches

6) Security

7) Real world examples

Implement Runtime Environments for HSA using LLVM

Implement Runtime Environments for HSA using LLVMNational Cheng Kung University * Transition to heterogeneous

- mobile phone to data centre

* LLVM and HSA

* HSA driven computing environment

Ubuntu

UbuntuJacquiline Tabelin The document provides information about the Ubuntu operating system. It discusses Ubuntu's history as a fork of Debian Linux that was created to be more user-friendly. It was founded by Mark Shuttleworth in 2004. The document also covers Ubuntu's design principles, use of the Linux kernel for processes, memory management, file systems, security features, and graphical user interface.

Similar to Optimizing shared caches in chip multiprocessors (20)

[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

![[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)](https://cdn.slidesharecdn.com/ss_thumbnails/cs264201107-mpi0mq-110308182928-phpapp02-thumbnail.jpg?width=560&fit=bounds)

[Harvard CS264] 07 - GPU Cluster Programming (MPI & ZeroMQ)npinto This document summarizes an MIT lecture on GPU cluster programming using MPI. It provides administrative details such as homework due dates and project information. It also announces various donations of computing resources for the class, including Amazon AWS credits and a Tesla graphics card for the best project. The lecture outline covers the problem of computations too large for a single CPU, an introduction to MPI, MPI basics, using MPI with CUDA, and other parallel programming approaches.

Massively Parallel Architectures

Massively Parallel ArchitecturesJason Hearne-McGuiness This document discusses massively parallel architectures and processing in memory (PIM) as ways to overcome the memory wall problem. It describes several PIM and cellular architectures including Cyclops, Gilgamesh, Shamrock, picoChip and DIMES. DIMES is an FPGA implementation of a simplified cellular architecture that was used by Jason McGuiness to test programming approaches. The talk concludes with an invitation for questions.

Introduction to multi core

Introduction to multi coremukul bhardwaj This document provides an introduction to multi-core processors. It discusses that a multi-core processor contains two or more processors on a single integrated circuit. This leads to enhanced performance, reduced power consumption, and more efficient simultaneous processing of multiple tasks. However, developing multithreaded applications for multi-core processors can be difficult, time-consuming, and error-prone. Adding more cores also introduces additional overheads and latencies between communicating and non-communicating cores. There are different types of multi-core architectures including symmetric multiprocessing (SMP) and asymmetric multiprocessing (AMP). Effective use of multi-core processors requires considerations around cache coherency, load balancing, interrupt handling, and concurrency management.

Cache coherence ppt

Cache coherence pptArendraSingh2 This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.

Leveraging Structured Data To Reduce Disk, IO & Network Bandwidth

Leveraging Structured Data To Reduce Disk, IO & Network BandwidthPerforce Most of the data that is pulled out of an SCM like Perforce Helix is common across multiple workspaces. Leveraging this fact means only fetching the data once from the repository. By creating cheap copies or clones of this data on demand, it is possible to dramatically reduce the load on the network, disks and Perforce servers, while making near-instant workspaces available to users.

Pdc lecture1

Pdc lecture1SyedSafeer1 This document provides an overview of parallel and distributed systems. It discusses that a parallel computer contains multiple processing elements that communicate and cooperate to solve problems quickly, while a distributed system contains independent computers that appear as a single system. It notes that parallel computers are implicitly distributed systems. It then discusses reasons for using parallel and distributed computing like Moore's law and limitations of sequential processing due to power and latency walls. Finally, it outlines some topics that will be covered in the course like different parallel computing platforms, programming paradigms, and challenges in parallel and distributed systems.

12-6810-12.ppt

12-6810-12.pptLonewolf379705 This document discusses cache hierarchies and techniques to improve cache performance. It covers types of cache misses like compulsory, capacity and conflict misses. Methods to reduce miss rates include using larger block sizes, caches and associativity. Victim caches and prefetching can help tolerate miss penalties. The document provides examples of Intel cache designs including a dual-core chip with private 12MB L3 caches and an 80-core prototype with an entire die of stacked SRAM cache. Non-uniform cache architectures are discussed as an approach for large multi-megabyte caches.

MT48 A Flash into the future of storage…. Flash meets Persistent Memory: The...

MT48 A Flash into the future of storage…. Flash meets Persistent Memory: The...Dell EMC World Several key technology trends are redefining the boundaries of the traditional storage infrastructure stack: In a rapidly changing world of system interconnects, emerging memory media, and storage semantics, Server Designers and Storage Architects are engaging and collaborating like never before to exploit breakthrough technology capabilities.

With the backdrop of Big Data volume, Cloud Data ubiquity and IoT Data velocity, Application Developers are entering the Post-POSIX world of real-time, high-frequency, low latency data management frameworks.

This session will address key technology trends in Storage, Networking, and Compute, as they define the parameters of a Memory Centric Architecture (MCA) and the Next Generation Data Center.

PyData Paris 2015 - Closing keynote Francesc Alted

PyData Paris 2015 - Closing keynote Francesc AltedPôle Systematic Paris-Region Francesc Alted (UberResearch GmbH), “New Trends In Storing And Analyzing Large Data Silos With Python”.

Bio: Teacher, developer and consultant in a wide variety of business applications. Particularly interested in the field of very large databases, with special emphasis in squeezing the last drop of performance out of computer as whole, i.e. not only the CPU, but the memory and I/O subsystems.

Webinar: OpenEBS - Still Free and now FASTEST Kubernetes storage

Webinar: OpenEBS - Still Free and now FASTEST Kubernetes storageMayaData Inc Webinar Session - https://youtu.be/_5MfGMf8PG4

In this webinar, we share how the Container Attached Storage pattern makes performance tuning more tractable, by giving each workload its own storage system, thereby decreasing the variables needed to understand and tune performance.

We then introduce MayaStor, a breakthrough in the use of containers and Kubernetes as a data plane. MayaStor is the first containerized data engine available that delivers near the theoretical maximum performance of underlying systems. MayaStor performance scales with the underlying hardware and has been shown, for example, to deliver in excess of 10 million IOPS in a particular environment.

Chap1

Chap1adisi An operating system provides an interface between users and computer hardware. It implements a virtual machine that is easier and safer to program than raw hardware. The key functions of an operating system include resource management, coordination of applications and users, and providing protection between processes. Operating systems abstract away hardware complexity and provide standard services to applications through virtualization layers. They juggle resources to provide the illusion of dedicated hardware and protect users from each other through mechanisms like address translation and dual mode operation.

Preparing OpenSHMEM for Exascale

Preparing OpenSHMEM for Exascaleinside-BigData.com In this video from the 2015 Stanford HPC Conference, Pavel Shamis from ORNL presents: Preparing OpenSHMEM for Exascale.

"OpenSHMEM is a partitioned global address space (PGAS) one-sided communications library that enables remote memory access (RMA) across processing elements (PEs). Its API allows data to be transferred from one PE memory space to another PE’s symmetric memory space; decoupling the data transfers from synchronizations. OpenSHMEM is useful for applications that are latency driven or that have irregular communication patterns, because its one-sided API can be mapped very efficiently to hardware (e.g. RDMA interconnects, etc), and its one-sided programming model helps the overlapping of communication with computation. Summit is Oak Ridge National Laboratory’s next high performance supercomputer system that will be based on a many core/GPU hybrid architecture. In order to prepare OpenSHMEM for future systems, it is important to enhance its programming model to enable efficient utilization of the new hardware capabilities (e.g. massive multithreaded systems, accesses different type memories, next generation of interconnects, etc). This session will present recent advances in the area of OpenSHMEM extensions, implementations, and tools.”

Watch the video: http://insidehpc.com/2015/02/video-preparing-openshmem-for-exascale/

See more talks in the Stanford HPC Conference Video Gallery: http://wp.me/P3RLHQ-dOO

Ceg4131 models

Ceg4131 modelsanandme07 This document discusses various models of parallel computer architectures. It begins with an overview of Flynn's taxonomy, which classifies computer systems based on the number of instruction and data streams. The main categories are SISD, SIMD, MIMD, and MISD. It then covers parallel computer models in more detail, including shared-memory multiprocessors, distributed-memory multicomputers, classifications based on interconnection networks and parallelism. It provides examples of different parallel architectures and references papers on advanced computer architecture and parallel processing.

Chorus - Distributed Operating System [ case study ]![Chorus - Distributed Operating System [ case study ]](https://cdn.slidesharecdn.com/ss_thumbnails/chorus-171117082036-181113144303-thumbnail.jpg?width=560&fit=bounds)

![Chorus - Distributed Operating System [ case study ]](https://cdn.slidesharecdn.com/ss_thumbnails/chorus-171117082036-181113144303-thumbnail.jpg?width=560&fit=bounds)

![Chorus - Distributed Operating System [ case study ]](https://cdn.slidesharecdn.com/ss_thumbnails/chorus-171117082036-181113144303-thumbnail.jpg?width=560&fit=bounds)

![Chorus - Distributed Operating System [ case study ]](https://cdn.slidesharecdn.com/ss_thumbnails/chorus-171117082036-181113144303-thumbnail.jpg?width=560&fit=bounds)

Chorus - Distributed Operating System [ case study ]Akhil Nadh PC

ChorusOS is a microkernel real-time operating system designed as a message-based computational model. ChorusOS started as the Chorus distributed real-time operating system research project at Institut National de Recherche en Informatique et Automatique (INRIA) in France in 1979. During the 1980s, Chorus was one of two earliest microkernels (the other being Mach) and was developed commercially by Chorus Systèmes. Over time, development effort shifted away from distribution aspects to real-time for embedded systems.

module4.ppt

module4.pptSubhasis Dash This document provides an introduction to multiprocessor systems and discusses different multiprocessor architectures including shared memory, distributed memory, and distributed shared memory systems. It describes the key differences between Uniform Memory Access (UMA) and Non-Uniform Memory Access (NUMA) models. Cache coherence problems that can arise in shared memory systems are discussed along with solutions like snooping and directory-based cache coherence protocols.

Using the big guns: Advanced OS performance tools for troubleshooting databas...

Using the big guns: Advanced OS performance tools for troubleshooting databas...Nikolay Savvinov Using OS performance tools and basic alternatives to troubleshoot production database issues

The document discusses using Linux performance tools like pidstat, ps, and tracing tools like perf, systemtap, and dtrace to troubleshoot complex database problems that may involve issues at the operating system, hardware, or network level. It provides examples of using these tools to diagnose specific issues like memory fragmentation, I/O problems, and network congestion and presents a methodology around reproducing issues, analyzing tool output, identifying root causes, and developing solutions.

Ad

More from Hoang Nguyen (20)

Rest api to integrate with your site

Rest api to integrate with your siteHoang Nguyen This document discusses Easyrec, an open source recommender engine that provides recommendations based on user actions like views, purchases, and ratings of products. It has an API that allows integrating recommendations into a website by passing a user ID and token. The API can take in user data and return recommendations based on what other similar users viewed, purchased, or rated highly. While Easyrec is easy to use, it has limitations in flexibility and only supports collaborative filtering recommendations.

How to build a rest api

How to build a rest apiHoang Nguyen This document outlines an agenda to introduce REST and building APIs with ASP.NET Web API. It begins with a quick demo, then discusses what REST is as an architectural style based on HTTP using resources and verbs. It covers HTTP concepts like requests, responses and status codes. Finally, it demonstrates building a REST API with ASP.NET Web API and discusses advantages of REST like using the well-defined HTTP protocol and enabling caching.

Api crash

Api crashHoang Nguyen This document provides an overview of APIs, including what they are, why they are useful, common data formats like JSON and XML, RESTful API design principles, and how to consume and create APIs. It discusses API concepts like resources, HTTP verbs, caching, authentication, and error handling. It also provides examples of consuming APIs with tools like Postman and creating a simple API in Node.js.

Smm and caching

Smm and cachingHoang Nguyen This document discusses caching and the SMRR mechanism introduced by Intel to prevent cache poisoning attacks on SMRAM. It explains that:

1) Memory caching types like write-back can allow data in CPU caches to be modified without writing to physical memory.

2) Early researchers exploited this to poison SMRAM caches and gain unauthorized access to protected memory.

3) Intel addressed this with the System Management Range Register (SMRR) that defines a restricted memory range for SMRAM and prevents caching of that memory when not in SMM.

How analysis services caching works

How analysis services caching worksHoang Nguyen This document discusses how Analysis Services caching works and provides strategies for warming the Storage Engine cache and Formula Engine cache. It explains that the Storage Engine handles data retrieval from disk while the Formula Engine determines which data is needed for queries. Caching can improve performance but requires understanding when Analysis Services is unable to cache data. The document recommends using the CREATE CACHE statement and running regular queries to pre-populate the caches with commonly used data. Memory usage must also be considered when warming the caches.

Hardware managed cache

Hardware managed cacheHoang Nguyen The document proposes optimizing DRAM caches for latency rather than hit rate. It summarizes previous work on DRAM caches like Loh-Hill Cache that treated DRAM cache similarly to SRAM cache. This led to high latency and low bandwidth utilization.

The document introduces the Alloy Cache design which avoids tag serialization and keeps tags and data in the same DRAM row for lower latency. It also proposes a Memory Access Predictor to selectively use parallel or serial access models for the lowest latency. Simulation results show Alloy Cache with a predictor outperforms previous designs like SRAM-Tags. The design achieves most of the potential latency benefits with a simple approach.

Directory based cache coherence

Directory based cache coherenceHoang Nguyen The document discusses non-uniform cache architectures (NUCA), cache coherence, and different implementations of directories in multicore systems. It describes NUCA designs that map data to banks based on distance from the controller to exploit non-uniform access times. Cache coherence is maintained using directory-based protocols that track copies of cache blocks. Directories can be implemented off-chip in DRAM or on-chip using duplicate tag stores or distributing the directory among cache banks. Examples of systems like SGI Origin2000 and Tilera Tile64 that use these techniques are also outlined.

Cache recap

Cache recapHoang Nguyen The document discusses memory hierarchy and caching techniques. It begins by explaining the need for a memory hierarchy due to differing access times of memory technologies like SRAM, DRAM, and disk. It then covers concepts like cache hits, misses, block size, direct mapping, set associativity, compulsory misses, capacity misses, and conflict misses. Finally, it discusses using a second-level cache to reduce memory access times by capturing misses from the first-level cache.

Python your new best friend

Python your new best friendHoang Nguyen This document provides an introduction to Python programming for astronomers. It discusses:

- Setting up the Python environment and selecting the correct version (2.6/2.7 vs 3.x)

- Why Python is popular for astronomy (free, packages like CASA are in Python)

- Getting started with Python scripts and the Python interpreter

- Important syntax aspects like indentation, importing modules, and creating functions

- Examples of useful Python modules for astronomy like NumPy, SciPy, Matplotlib, and Astropy

Python language data types

Python language data typesHoang Nguyen This document provides an introduction to the Python language and discusses Python data types. It covers how to install Python, interact with the Python interpreter through command line and IDLE modes, and learn basic Python parts like data types, operators, functions, and control structures. The document discusses numeric, string, and other data types in Python and how to manipulate them using built-in functions and operators. It also introduces Python library modules and the arcpy package for geoprocessing in ArcGIS.

Python basics

Python basicsHoang Nguyen A program is a sequence of instructions that are run by the processor. To run a program, it must be compiled into binary code and given to the operating system. The OS then gives the code to the processor to execute. Functions allow code to be reused by defining operations and optionally returning values. Strings are sequences of characters that can be manipulated using indexes and methods. Common string methods include upper() and concatenation using +.

Programming for engineers in python

Programming for engineers in pythonHoang Nguyen This document provides an agenda and notes for a programming lecture. The lecture covers sample problems, hash functions and dictionaries, simulating a car, functions as arguments, checking Fermat's Last Theorem, cumulative sums, estimating e and pi through Taylor expansions, finding words with triple double letters, PyGame for game development, and developing a single-player and two-player car game in PyGame. The document includes code examples and references to further resources.

Learning python

Learning pythonHoang Nguyen Python is a multi-paradigm programming language that is object-oriented, imperative and functional. It is dynamically typed, with support for complex data types like lists and strings. Python code is commonly written and executed using the interactive development environment IDLE.

Extending burp with python

Extending burp with pythonHoang Nguyen 1. Burp extensions can overcome web application hurdles through the Burp API. Interfaces like IMessageEditorTab and ITab allow creating new views of requests and responses, while processHTTPMessage and doPassiveScan can automate tasks by catching and rewriting traffic.

2. Examples include decoding custom encodings, signing requests, viewing unique response headers, and passively scanning for encoded values in cookies. Common problems are solved with minimal Python coding against the Burp API.

Cobol, lisp, and python

Cobol, lisp, and pythonHoang Nguyen The document provides information on three programming languages: COBOL, LISP, and Python. COBOL was released in 1959 and was used for 80% of business transactions due to its reliability. LISP was the second high-level language created in 1958 and introduced innovations like garbage collection and recursion using linked lists. Python was developed in the 1990s and prioritizes readability through features like whitespace and a simple grammar.

Object oriented programming using c++

Object oriented programming using c++Hoang Nguyen Object-oriented programming uses abstraction and encapsulation through abstract data types (ADTs). An ADT defines a data type and its interface independently of its implementation. This allows information hiding and modular program design. Common languages like C++, Java, and Ruby support ADTs through classes or modules, which package data with methods, support inheritance and polymorphism, and provide visibility control through private/public access specifiers. Parameterized ADTs allow a data type to work with different element types. Namespaces and packages provide separate scopes to avoid naming conflicts.

Object oriented analysis

Object oriented analysisHoang Nguyen Object-oriented analysis and design (OOAD) emphasizes investigating requirements rather than solutions, and conceptual solutions that fulfill requirements rather than implementations. OOAD focuses on identifying domain concepts and defining software objects and how they collaborate. The unified process model includes inception, elaboration, construction, and transition phases with iterations and milestones leading to final product releases. Main OO concepts are encapsulation, abstraction, inheritance, and polymorphism.

Object model

Object modelHoang Nguyen The document discusses the key elements of the object model, including abstraction, encapsulation, modularity, and hierarchy. It explains that abstraction is one of the fundamental ways to cope with complexity in software design. Abstraction focuses on the essential characteristics of an object that distinguish it from other objects, from the perspective of the viewer. The object model provides a conceptual framework for object-oriented programming that is based on these elements.

Data structures and algorithms

Data structures and algorithmsHoang Nguyen The document discusses abstract data types (ADTs), specifically queues. It defines a queue as a linear collection where elements are added to one end and removed from the other end, following a first-in, first-out (FIFO) approach. The key queue operations are enqueue, which adds an element, and dequeue, which removes the element that has been in the queue longest. Queues can be implemented using arrays or linked lists.

Data abstraction the walls

Data abstraction the wallsHoang Nguyen The document discusses abstract data types (ADTs) and their implementation in C++. It describes how ADTs use encapsulation, inheritance and polymorphism to separate a data structure from its implementation. This allows operations on a data type to be defined independently of how its data is stored. The document also covers how C++ classes can be used to implement ADTs by bundling related data and functions into objects that hide their underlying representations. Exceptions are discussed as a mechanism for handling errors during program execution.

Ad

Recently uploaded (20)

Increasing Retail Store Efficiency How can Planograms Save Time and Money.pptx

Increasing Retail Store Efficiency How can Planograms Save Time and Money.pptxAnoop Ashok In today's fast-paced retail environment, efficiency is key. Every minute counts, and every penny matters. One tool that can significantly boost your store's efficiency is a well-executed planogram. These visual merchandising blueprints not only enhance store layouts but also save time and money in the process.

TrsLabs - Fintech Product & Business Consulting

TrsLabs - Fintech Product & Business ConsultingTrs Labs Hybrid Growth Mandate Model with TrsLabs

Strategic Investments, Inorganic Growth, Business Model Pivoting are critical activities that business don't do/change everyday. In cases like this, it may benefit your business to choose a temporary external consultant.

An unbiased plan driven by clearcut deliverables, market dynamics and without the influence of your internal office equations empower business leaders to make right choices.

Getting things done within a budget within a timeframe is key to Growing Business - No matter whether you are a start-up or a big company

Talk to us & Unlock the competitive advantage

Andrew Marnell: Transforming Business Strategy Through Data-Driven Insights

Andrew Marnell: Transforming Business Strategy Through Data-Driven InsightsAndrew Marnell With expertise in data architecture, performance tracking, and revenue forecasting, Andrew Marnell plays a vital role in aligning business strategies with data insights. Andrew Marnell’s ability to lead cross-functional teams ensures businesses achieve sustainable growth and operational excellence.

Quantum Computing Quick Research Guide by Arthur Morgan

Quantum Computing Quick Research Guide by Arthur MorganArthur Morgan This is a Quick Research Guide (QRG).

QRGs include the following:

- A brief, high-level overview of the QRG topic.

- A milestone timeline for the QRG topic.

- Links to various free online resource materials to provide a deeper dive into the QRG topic.

- Conclusion and a recommendation for at least two books available in the SJPL system on the QRG topic.

QRGs planned for the series:

- Artificial Intelligence QRG

- Quantum Computing QRG

- Big Data Analytics QRG

- Spacecraft Guidance, Navigation & Control QRG (coming 2026)

- UK Home Computing & The Birth of ARM QRG (coming 2027)

Any questions or comments?

- Please contact Arthur Morgan at [email protected].

100% human made.

HCL Nomad Web – Best Practices und Verwaltung von Multiuser-Umgebungen

HCL Nomad Web – Best Practices und Verwaltung von Multiuser-Umgebungenpanagenda Webinar Recording: https://www.panagenda.com/webinars/hcl-nomad-web-best-practices-und-verwaltung-von-multiuser-umgebungen/

HCL Nomad Web wird als die nächste Generation des HCL Notes-Clients gefeiert und bietet zahlreiche Vorteile, wie die Beseitigung des Bedarfs an Paketierung, Verteilung und Installation. Nomad Web-Client-Updates werden “automatisch” im Hintergrund installiert, was den administrativen Aufwand im Vergleich zu traditionellen HCL Notes-Clients erheblich reduziert. Allerdings stellt die Fehlerbehebung in Nomad Web im Vergleich zum Notes-Client einzigartige Herausforderungen dar.

Begleiten Sie Christoph und Marc, während sie demonstrieren, wie der Fehlerbehebungsprozess in HCL Nomad Web vereinfacht werden kann, um eine reibungslose und effiziente Benutzererfahrung zu gewährleisten.

In diesem Webinar werden wir effektive Strategien zur Diagnose und Lösung häufiger Probleme in HCL Nomad Web untersuchen, einschließlich

- Zugriff auf die Konsole

- Auffinden und Interpretieren von Protokolldateien

- Zugriff auf den Datenordner im Cache des Browsers (unter Verwendung von OPFS)

- Verständnis der Unterschiede zwischen Einzel- und Mehrbenutzerszenarien

- Nutzung der Client Clocking-Funktion

IEDM 2024 Tutorial2_Advances in CMOS Technologies and Future Directions for C...

IEDM 2024 Tutorial2_Advances in CMOS Technologies and Future Directions for C...organizerofv IEDM 2024 Tutorial2

Enhancing ICU Intelligence: How Our Functional Testing Enabled a Healthcare I...

Enhancing ICU Intelligence: How Our Functional Testing Enabled a Healthcare I...Impelsys Inc. Impelsys provided a robust testing solution, leveraging a risk-based and requirement-mapped approach to validate ICU Connect and CritiXpert. A well-defined test suite was developed to assess data communication, clinical data collection, transformation, and visualization across integrated devices.

Heap, Types of Heap, Insertion and Deletion

Heap, Types of Heap, Insertion and DeletionJaydeep Kale This pdf will explain what is heap, its type, insertion and deletion in heap and Heap sort

Technology Trends in 2025: AI and Big Data Analytics

Technology Trends in 2025: AI and Big Data AnalyticsInData Labs At InData Labs, we have been keeping an ear to the ground, looking out for AI-enabled digital transformation trends coming our way in 2025. Our report will provide a look into the technology landscape of the future, including:

-Artificial Intelligence Market Overview

-Strategies for AI Adoption in 2025

-Anticipated drivers of AI adoption and transformative technologies

-Benefits of AI and Big data for your business

-Tips on how to prepare your business for innovation

-AI and data privacy: Strategies for securing data privacy in AI models, etc.

Download your free copy nowand implement the key findings to improve your business.

Linux Professional Institute LPIC-1 Exam.pdf

Linux Professional Institute LPIC-1 Exam.pdfRHCSA Guru Introduction to LPIC-1 Exam - overview, exam details, price and job opportunities

Semantic Cultivators : The Critical Future Role to Enable AI

Semantic Cultivators : The Critical Future Role to Enable AIartmondano By 2026, AI agents will consume 10x more enterprise data than humans, but with none of the contextual understanding that prevents catastrophic misinterpretations.

AI EngineHost Review: Revolutionary USA Datacenter-Based Hosting with NVIDIA ...

AI EngineHost Review: Revolutionary USA Datacenter-Based Hosting with NVIDIA ...SOFTTECHHUB I started my online journey with several hosting services before stumbling upon Ai EngineHost. At first, the idea of paying one fee and getting lifetime access seemed too good to pass up. The platform is built on reliable US-based servers, ensuring your projects run at high speeds and remain safe. Let me take you step by step through its benefits and features as I explain why this hosting solution is a perfect fit for digital entrepreneurs.

UiPath Community Berlin: Orchestrator API, Swagger, and Test Manager API

UiPath Community Berlin: Orchestrator API, Swagger, and Test Manager APIUiPathCommunity Join this UiPath Community Berlin meetup to explore the Orchestrator API, Swagger interface, and the Test Manager API. Learn how to leverage these tools to streamline automation, enhance testing, and integrate more efficiently with UiPath. Perfect for developers, testers, and automation enthusiasts!

📕 Agenda

Welcome & Introductions

Orchestrator API Overview

Exploring the Swagger Interface

Test Manager API Highlights

Streamlining Automation & Testing with APIs (Demo)

Q&A and Open Discussion

Perfect for developers, testers, and automation enthusiasts!

👉 Join our UiPath Community Berlin chapter: https://community.uipath.com/berlin/

This session streamed live on April 29, 2025, 18:00 CET.

Check out all our upcoming UiPath Community sessions at https://community.uipath.com/events/.

Complete Guide to Advanced Logistics Management Software in Riyadh.pdf

Complete Guide to Advanced Logistics Management Software in Riyadh.pdfSoftware Company Explore the benefits and features of advanced logistics management software for businesses in Riyadh. This guide delves into the latest technologies, from real-time tracking and route optimization to warehouse management and inventory control, helping businesses streamline their logistics operations and reduce costs. Learn how implementing the right software solution can enhance efficiency, improve customer satisfaction, and provide a competitive edge in the growing logistics sector of Riyadh.

Generative Artificial Intelligence (GenAI) in Business

Generative Artificial Intelligence (GenAI) in BusinessDr. Tathagat Varma My talk for the Indian School of Business (ISB) Emerging Leaders Program Cohort 9. In this talk, I discussed key issues around adoption of GenAI in business - benefits, opportunities and limitations. I also discussed how my research on Theory of Cognitive Chasms helps address some of these issues

Massive Power Outage Hits Spain, Portugal, and France: Causes, Impact, and On...

Massive Power Outage Hits Spain, Portugal, and France: Causes, Impact, and On...Aqusag Technologies In late April 2025, a significant portion of Europe, particularly Spain, Portugal, and parts of southern France, experienced widespread, rolling power outages that continue to affect millions of residents, businesses, and infrastructure systems.

Mobile App Development Company in Saudi Arabia

Mobile App Development Company in Saudi ArabiaSteve Jonas EmizenTech is a globally recognized software development company, proudly serving businesses since 2013. With over 11+ years of industry experience and a team of 200+ skilled professionals, we have successfully delivered 1200+ projects across various sectors. As a leading Mobile App Development Company In Saudi Arabia we offer end-to-end solutions for iOS, Android, and cross-platform applications. Our apps are known for their user-friendly interfaces, scalability, high performance, and strong security features. We tailor each mobile application to meet the unique needs of different industries, ensuring a seamless user experience. EmizenTech is committed to turning your vision into a powerful digital product that drives growth, innovation, and long-term success in the competitive mobile landscape of Saudi Arabia.

Transcript: #StandardsGoals for 2025: Standards & certification roundup - Tec...

Transcript: #StandardsGoals for 2025: Standards & certification roundup - Tec...BookNet Canada Book industry standards are evolving rapidly. In the first part of this session, we’ll share an overview of key developments from 2024 and the early months of 2025. Then, BookNet’s resident standards expert, Tom Richardson, and CEO, Lauren Stewart, have a forward-looking conversation about what’s next.

Link to recording, presentation slides, and accompanying resource: https://bnctechforum.ca/sessions/standardsgoals-for-2025-standards-certification-roundup/

Presented by BookNet Canada on May 6, 2025 with support from the Department of Canadian Heritage.

Optimizing shared caches in chip multiprocessors

- 1. Core 2 Duo die “Just a few years ago, the idea of putting multiple processors on a chip was farfetched. Now it is accepted and commonplace, and virtually every new high performance processor is a chip multiprocessor of some sort…” Center for Electronic System Design Univ. of California Berkeley Chip Multiprocessors?? “Mowry is working on the development of single-chip multiprocessors: one large chip capable of performing multiple operations at once, using similar techniques to maximize performance” -- Technology Review, 1999 Sony's Playstation 3, 2006

- 2. CMP Caches: Design Space • Architecture – Placement of Cache/Processors – Interconnects/Routing • Cache Organization & Management – Private/Shared/Hybrid – Fully Hardware/OS Interface “L2 is the last line of defense before hitting the memory wall, and is the focus of our talk”

- 3. Private L2 Cache I$ D$ I$ D$ L2 $ L2 $ L2 $ L2 $ L2 $ L2 $ I N T E R C O N N E C T Coherence Protocol Offchip Memory + Less interconnect traffic + Insulates L2 units + Hit latency – Duplication – Load imbalance – Complexity of coherence – Higher miss rate L1 L1 Proc

- 4. Shared-Interleaved L2 Cache – Interconnect traffic – Interference between cores – Hit latency is higher + No duplication + Balance the load + Lower miss rate + Simplicity of coherence I$ D$ I$ D$ I N T E R C O N N E C T Coherence ProtocolL1 L2

- 5. Take Home Message • Leverage on-chip access time

- 6. Take Home Messages • Leverage on-chip access time • Better sharing of cache resources • Isolating performance of processors • Place data on the chip close to where it is used • Minimize inter-processor misses (in shared cache) • Fairness towards processors

- 7. On to some solutions… Jichuan Chang and Gurindar S. Sohi Cooperative Caching for Chip Multiprocessors International Symposium on Computer Architecture, 2006. Nikos Hardavellas, Michael Ferdman, Babak Falsafi, and Anastasia Ailamaki Reactive NUCA: Near-Optimal Block Placement and Replication in Distributed Caches International Symposium on Computer Architecture, 2009. Shekhar Srikantaiah, Mahmut Kandemir, and Mary Jane Irwin Adaptive Set-Pinning: Managing Shared Caches in Chip Multiprocessors Architectural Support for Programming Languages and Operating, Systems 2008. each handles this problem in a different way

- 8. Co-operative Caching (Chang & Sohi) • Private L2 caches • Attract data locally to reduce remote on chip access. Lowers average on-chip misses. • Co-operation among the private caches for efficient use of resources on the chip. • Controlling the extent of co-operation to suit the dynamic workload behavior

- 9. CC Techniques • Cache to cache transfer of clean data – In case of miss transfer “clean” blocks from another L2 cache. – This is useful in the case of “read only” data (instructions) . • Replication aware data replacement – Singlet/Replicate. – Evict singlet only when no replicates exist. – Singlets can be “spilled” to other cache banks. • Global replacement of inactive data – Global management needed for managing “spilling”. – N-Chance Forwarding. – Set recirculation count to N when spilled. – Decrease N by 1 when spilled again, unless N becomes 0.

- 10. Set “Pinning” -- Setup P1 P2 P3 P4 Set 0 Set 1 : : Set (S-1) L1 cache Processors Shared L2 cache I n t e r c o n n e c t Main Memory

- 11. Set “Pinning” -- Problem P1 P2 P3 P4 Set 0 Set 1 : : Set (S-1) Main Memory

- 12. Set “Pinning” -- Types of Cache Misses • Compulsory (aka Cold) • Capacity • Conflict • Coherence • Compulsory • Inter-processor • Intra-processor versus

- 13. P1 P2 P3 P4 Main Memory POP 1 POP 2 POP 3 POP 4 Set : : Set Owner Other bits Data

- 14. R-NUCA: Use Class-Based Strategies Solve for the common case! Most current (and future) programs have the following types of accesses 1. Instruction Access – Shared, but Read-Only 2. Private Data Access – Read-Write, but not Shared 3. Shared Data Access – Read-Write (or) Read-Only, but Shared.

- 15. R-NUCA: Can do this online! • We have information from the OS and TLB • For each memory block, classify it as – Instruction – Private Data – Shared Data • Handle them differently – Replicate instructions – Keep private data locally – Keep shared data globally

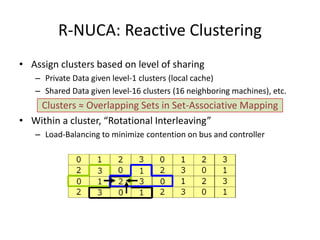

- 16. R-NUCA: Reactive Clustering • Assign clusters based on level of sharing – Private Data given level-1 clusters (local cache) – Shared Data given level-16 clusters (16 neighboring machines), etc. Clusters ≈ Overlapping Sets in Set-Associative Mapping • Within a cluster, “Rotational Interleaving” – Load-Balancing to minimize contention on bus and controller

- 17. Future Directions Area has been closed.

- 18. Just Kidding… • Optimize for Power Consumption • Assess trade-offs between more caches and more cores • Minimize usage of OS, but still retain flexibility • Application adaptation to allocated cache quotas • Adding hardware directed thread level speculation

- 20. Backup • Commercial and research prototypes – Sun MAJC – Piranha – IBM Power 4/5 – Stanford Hydra

- 21. Backup