Ad

System design using HDL - Module 1

- 4. SYSTEM DESIGN USING HDL (ECE43) # Digital system design using Verilog, Charles Roth, Lizy Kurian John, Byeong Kil Lee, 1st Edition, 2016, Cengage Learning 1 2.1, 2.2, 2.3 - 2.8, 2.11, 2.13 - 2.15 2 2.9, 2.10, 2.12, 2.16 - 2.19, 8.1, 8.2 3 3.1 - 3.4, 5.1, 5.2.1, 5.3 4 4.1 - 4.5, 4.8, 4.6, 4.7, 4.9, 4.11 5 6.1 - 6.5, 6.7 - 6.12

- 5. 21/01/2019 Aravinda K., Dept. of E&C, NHCE 5 CO1 Identify the necessity of HDL for the automation of VLSI design CO2 Select Verilog for EDA, and describe its structure and syntax CO3 Apply the concepts of HDL on programmable devices, such as CPLD and FPGA CO4 Translate the design on state machine into HDL program CO5 Write optimized HDL codes for simple and complex systems CO6 Employ the FPGA hardware for the implementation of the HDL codes COURSE OUTCOMES

- 6. Term Year Number of gates Examples SSI 1961 Upto 20 logic gates Flip-flops, Decoders, Registers MSI 1966 20 till 200 gates Multiplexers, Adders, Counters LSI 1971 200 till 10,000 8-bit Microprocessors, RAM, ROM VLSI 1980 10,000 till 1,00,000 Microcontrollers, 16 & 32-bit Microprocessors, DRAM ULSI 1990 Above 1,00,000 gates 64-bit Microprocessors, DSPs, SoC 21/01/2019 6Aravinda K., Dept. of E&C, NHCE MODULE-1: INTRODUCTION TO VERILOG

- 7. 21/01/2019 Aravinda K., Dept. of E&C, NHCE 7 DESIGN ENTRY Schematic capture: Lower level of abstraction (gates, flip-flops, standard MSI building blocks) HDL: Higher level of abstraction - (behavioral: flow-chart, algorithm) (structural: specific components or implementations) SYNTHESIS Process of conversion of higher-level abstraction of the design into actual components at the gate & flip-flop levels. The output of the synthesis tool is the netlist, which is a list of gates and a list of their interconnections. As the synthesis tool converts the design descriptions into hardware, it is also called as “design compiler” or “silicon compiler”.

- 8. 21/01/2019 8Aravinda K., Dept. of E&C, NHCE

- 9. 21/01/2019 9Aravinda K., Dept. of E&C, NHCE

- 10. 21/01/2019 10Aravinda K., Dept. of E&C, NHCE

- 11. 21/01/2019 11Aravinda K., Dept. of E&C, NHCE After the post-synthesis simulation, the design can be implemented in several different target technologies (device lengths). The target could be a completely custom IC, or could be implemented using the standard parts that are available from the vendor. The standard parts are at the lowest level of sophistication and density, with the usage of old- fashioned printed circuit board. The fully-custom ASIC is at the highest level of density and performance. The other devices such as CPLD and FPGA come in between, as programmable solutions.

- 12. 21/01/2019 12Aravinda K., Dept. of E&C, NHCE

- 13. 21/01/2019 13Aravinda K., Dept. of E&C, NHCE The current two most common target technologies are FPGAs and ASICs. The design is mapped into the specific target technology (channel length), and placed into specific parts in the target ASIC or FPGA. During routing, the selected components are connected to each other, using the available paths. In case of an ASIC, the routed design is utilized for generating a photo-mask, which will be utilized for manufacturing the IC. In case of an FPGA, the routed design is translated into a bit file, for the programming of the selected cells inside the FPGA.

- 14. 21/01/2019 14Aravinda K., Dept. of E&C, NHCE

- 15. 21/01/2019 15Aravinda K., Dept. of E&C, NHCE

- 16. 21/01/2019 16Aravinda K., Dept. of E&C, NHCE HARDWARE DESCRIPTION LANGUAGES HDL is a textual method of documenting the circuits, and feeding them into the simulators in the textual form, as opposed to the graphic form. HDLs lead to a top-down design methodology (specified and tested at a high level), and HDLs are designed to be technology independent. HDLs can describe a digital system at three different levels – behavioral (functional description), data flow (logic equations) and structural (in terms of subcomponents).

- 17. 21/01/2019 17Aravinda K., Dept. of E&C, NHCE VHDL Verilog Government developed (Designed and sponsored by US department of defense), and became IEEE standard in 1987 Commercially developed (Designed by Gateway design system corporation), became IEEE standard in 1995 Strongly typecast, based on “Ada” language, and is case- insensitive Mildly typecast, based on “C” language, and is case-sensitive Structured, and is for large and complex systems (Difficult to learn, but more powerful) Simpler, with less syntax and fewer constructs (Easier to learn, and less powerful) Two popular HDLs are Verilog & VHDL. Verilog was a proprietary language in 1984, and was later owned and opened up by Cadence, in order to create a vendor-independent language specification, and to prevent the industry from shifting to VHDL.

- 18. 21/01/2019 18Aravinda K., Dept. of E&C, NHCE In addition, there are system design languages, such as System C and System Verilog, which describe large digital systems at a block level behavior. These languages are primarily used for verification and validation. They help in reducing the design cycle time for large systems; the design problems become evident in the early stages, instead of becoming obvious during system integration. When different blocks of a large system are designed by different teams, during the initial design process, one team can make use of the system level description of a block that is being designed by the other team. In addition to the system design languages, there are tools that have emerged, which can convert the models written in non-HDL, directly into hardware.

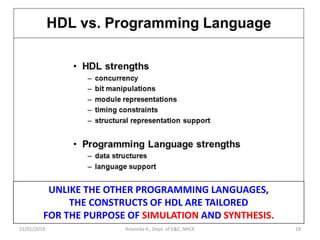

- 19. 21/01/2019 19Aravinda K., Dept. of E&C, NHCE UNLIKE THE OTHER PROGRAMMING LANGUAGES, THE CONSTRUCTS OF HDL ARE TAILORED FOR THE PURPOSE OF SIMULATION AND SYNTHESIS.

- 20. 21/01/2019 20Aravinda K., Dept. of E&C, NHCE Sl. no. Symbol Name 1 ~ Tilde 2 ‘ Tick (Grave) 3 ` Back-tick (Acute) 4 “ Quote 5 & Ampersand 6 ^ Caret 7 # Cross-hash (Sharp) 8 * Asterisk 9 ( Parenthesis 10 [ Bracket 11 { Brace 12 < Angle bracket 13 / Slash (Solidus) 14 Back-slash 15 | Pipe (Bar) 16 - Hyphen (Dash) 17 @ Astatine (At) 18 : Colon 19 , Comma (Apostrophe) 20 … Ellipsis 21 ! Exclamation (Bang) 22 _ Underscore 23 . Period 24 ; Semicolon COMMONLY USED SYMBOLS

- 21. 21/01/2019 21Aravinda K., Dept. of E&C, NHCE Verilog Description of Combinational Circuits The combinational circuits are always working simultaneously, and hence they are modeled in Verilog by concurrent statements or continuous assignments. Concurrent statements are always ready to execute, and hence, it is possible to simulate the execution of the several parts of the circuit at the same time. The Verilog simulator continuously monitors the right side of each concurrent statement, and whenever a signal changes, the expression on the right side gets immediately re-evaluated.

- 22. 21/01/2019 22Aravinda K., Dept. of E&C, NHCE #5 indicates a delay of 5 ns, representing the propagation delay of each logic gate. If it is not included, then the computation will be instantaneous. When the statements get executed, the variable “C” gets computed after 5 ns, and the variable “E” gets computed after another 5 ns, thus the total delay becoming as 10 ns. The order of the concurrent statements is not important. The output for the following will be the same as the previous one:

- 23. 21/01/2019 23Aravinda K., Dept. of E&C, NHCE In this example, when the gate delays have different values, the outputs also update at different times, even though the statements execute simultaneously. If A changes at a time-stamp of 5 ns, then D, E and F change at 7 ns, 6 ns and 8 ns respectively.

- 24. 21/01/2019 24Aravinda K., Dept. of E&C, NHCE “Delta delay” is an infinitesimally small delay, which is used to indicate the sequentiality between dependant concurrent statements. VHDL simulators display the delta delay, whereas Verilog simulators do not. The general form of the signal assignment statement is: The brackets indicate that the delay is optional.

- 25. 21/01/2019 25Aravinda K., Dept. of E&C, NHCE Statement Result assign #10 CLK= ~CLK; Waveform with name “CLK” is produced assign #10 Clk= ~Clk; Waveform with name “Clk” is produced assign CLK= ~CLK; The waveform will never advance A Verilog identifier or a signal name can contain letters, numbers, underscore character and dollar sign. A Verilog identifier must start with a letter or an underscore character. A Verilog identifier cannot start with a number or dollar sign. The dollar sign is reserved as the first character for the system tasks.

- 26. 21/01/2019 26Aravinda K., Dept. of E&C, NHCE Valid identifiers Invalid identifiers adder 4bit_adder Mux_input $100 _error_code always _$500 _#123 Every Verilog statement must be terminated with a semicolon. Anything following a double slash is treated as a comment to the end of the line. Comments for more than one line start with “/*” and end with “*/”. Words such as “and”, “or” and “always”, are reserved words.

- 27. 21/01/2019 27Aravinda K., Dept. of E&C, NHCE When the signal is of type wire (or net), it generally has a value of 0 or 1. The net values in Verilog are represented as - <number of bits>’<base><value>. Hence, 1’b0 means “1 position binary 0”. The decimal and hexadecimal values are represented with “d” and “h”. A one-dimensional array of bit signals is referred to as a vector. A 4 bit-wire can be named as vector B, and can be declared as, wire B[3:0];. The vector B has an index range 0 through 3, and its elements are designated as B[0], B[1], B[2] and B[3]. The statement B=4’b1100 assigns 1 to B[3], 1 to B[2], 0 to B[1] and 0 to B[0].

- 28. 21/01/2019 28Aravinda K., Dept. of E&C, NHCE “&&” is the logical AND operator “&” is the bitwise AND operator

- 29. 21/01/2019 29Aravinda K., Dept. of E&C, NHCE Verilog Modules A Module is a basic building block that declares input and output signals, and specifies the internal operation of the module. All the I/O signals have to be listed in the module statement. Since “C” is an internal signal, it has to be declared as wire.

- 30. 21/01/2019 30Aravinda K., Dept. of E&C, NHCE

- 31. 21/01/2019 31Aravinda K., Dept. of E&C, NHCE The interface ports can be of type input, output or inout. VHDL is very strict in compilation, wheras Verilog produces an output even when the variable is declared as input. However, a variable has to be declared as inout, if that variable is used by other modules.

- 32. 21/01/2019 32Aravinda K., Dept. of E&C, NHCE module FullAdder (X, Y, Cin, Cout, Sum); output Cout, Sum; input X, Y, Cin; assign #10 Sum = X ^ Y ^ Cin; assign #10 Cout = ( X && Y) || ( X && Cin) || ( Y && Cin); endmodule

- 33. 21/01/2019 33Aravinda K., Dept. of E&C, NHCE In the structural description, the 4-bit adder is declared as a module, and the full adder module is instantiated inside the 4-bit adder module. Here, each instance of Full adder has a port map, which corresponds one-to-one with the signals in the component port (FullAdder module). This method, in which the order of the signals in the portmap is same as the order of the signals in the ports of the module, is called as “positional association”. If the ports are mapped by name, then it is called as “named association”.

- 34. 21/01/2019 34Aravinda K., Dept. of E&C, NHCE Verilog Assignments Continuous Procedural Blocking Non-blockingExplicit Implicit Keyword: assign Keywords: initial, always

- 35. 21/01/2019 35Aravinda K., Dept. of E&C, NHCE

- 36. 21/01/2019 36Aravinda K., Dept. of E&C, NHCE Procedural Assignments Combinational logic constantly reacts to input changes, whereas synchronous sequential logic responds to changes that are dependent on the clock. Therefore, the procedural assignments are used to model the sequential logic, such as registers and finite state machines. Unlike the continuous assignments, with procedural assignments, the execution of statements happens with a sequence of operations. The two types of procedural assignment blocks in Verilog are “initial” and “always”; the LHS of the assignment statements, inside these blocks, have to be declared as of data type “reg”.

- 37. 21/01/2019 37Aravinda K., Dept. of E&C, NHCE initial always Executes only once Executes in a loop Executes without waiting Executes after an event Useful in simulation & verification Useful for synthesis

- 38. 21/01/2019 38Aravinda K., Dept. of E&C, NHCE

- 39. 21/01/2019 39Aravinda K., Dept. of E&C, NHCE In this example, assuming the initial values as: A=1’b1, B=1’b0, C=1’b1, D=1’b0, the outputs after completion of the execution are: A=1’b0, B=1’b0, C=1’b0, D=1’b1. We should be very careful while using “always” to represent combinational logic. If any input signals are accidentally omitted from the sensitivity list, there will be mismatches between simulation and synthesis outcomes. The statement “always @(*)” avoids such accidental errors.

- 40. 21/01/2019 40Aravinda K., Dept. of E&C, NHCE

- 41. 21/01/2019 41Aravinda K., Dept. of E&C, NHCE input and inout ports have to be of type “wire”; output ports can be of either “wire” or “reg” type. Here, D and E are declared as “reg”, as they are at LHS. Therefore, D cannot be declared as “inout”. When the sensitivity list contains “*”, the “always” block gets triggered for any input signal changes.

- 42. 21/01/2019 42Aravinda K., Dept. of E&C, NHCE Note 1. “wire” does not store information, whereas “reg” stores information. The initial value of a “wire” is “z” (high impedance), and that of “reg” is “x” (unknown). 2. The operator “=” has a blocking nature inside “always”, whereas it has a non-blocking (concurrent) nature outside “always”. 3. The operator “<=” has a non-blocking nature inside “always”, and has no usage as an assignment operator outside “always”. 4. The LHS elements inside the procedural blocks have to be declared as “reg” data type. But “reg” data type cannot be present at the LHS of a continuous assignment statement. 5. For synthesizable codes, it is better to use non-blocking assignments for sequential logic, and blocking assignments for combinational logic, and not to mix both in the same block.

- 43. 21/01/2019 43Aravinda K., Dept. of E&C, NHCE

- 44. 21/01/2019 44Aravinda K., Dept. of E&C, NHCE Modeling of flip-flops using “always” block When a rising edge of the clock occurs, Q is set equal to D. If the flip-flop has a delay of 5 ns, then the statement can be: Q <= #5 D; If Q changes when D changes, then it is a transparent latch. In this code, Q changes when G = 1. Either (G or D) or (G, D) are acceptable, in the sensitivity list. This flip-flop is with active-low asynchronous “clear” input. When clear = 0, the flip-flop is reset; otherwise, Q is updated with the rising edge of the clock.

- 45. 21/01/2019 45Aravinda K., Dept. of E&C, NHCE “if” statements cannot be used as concurrent. Brace indicates that any number of “else if” can be included. Bracket indicates that “else” is optional.

- 46. 21/01/2019 46Aravinda K., Dept. of E&C, NHCE J K Qn 0 0 Qn-1 0 1 0 1 0 1 1 1 Q’n-1 This flip-flop is with active-low asynchronous “preset” (SN) and “clear” (RN) inputs, and triggers on the falling edge of clock. The characteristic equation of the flip-flop is, Q+ = JQ’ + K’Q.

- 47. 21/01/2019 47Aravinda K., Dept. of E&C, NHCE “Qint” is defined as an internal signal because, RHS cannot have an output identifier, and inout type cannot be declared as reg. 8 ns represents the time taken to set or to clear, and 10 ns represents the time taken for Q to change. In the “if” statement, either (~RN) or (RN == 1’b0) are acceptable.

- 48. 21/01/2019 48Aravinda K., Dept. of E&C, NHCE “always” blocks using event control statements When sensitivity list is not specified or not required, event control statements such as “wait” can be used. In contrast, when wait statements are included, the always block cannot have sensitivity list. The wait statement is used as a level- sensitive event control. It can also be used to handshake between two processes.

- 49. 21/01/2019 49Aravinda K., Dept. of E&C, NHCE 1. (a) It will compile, but will not simulate correctly because, the “carry” statement has no dependency on “add” signal. 2. (d) It will not compile because, when compiler gets to “else”, it does not find the corresponding “if” before. Note: Both codes can be corrected by adding “begin” and “end”. 1 2 (a) It will compile, but will not simulate correctly. (b) It will compile and simulate, but will not synthesize correctly. (c) It will work correctly both in simulation and synthesis. (d) It will not get compiled at all.

- 50. 21/01/2019 50Aravinda K., Dept. of E&C, NHCE Verilog data types Net Variable Keywords wire (connections) tri (tristate) wand (wired and) wor (wired or) Keywords reg (register) time (stores timing) integer (without point) real (floating point) realtime (fractional time)

- 51. 21/01/2019 Aravinda K., Dept. of E&C, NHCE 51 wand and wor indicate that the net is being driven by more inputs; the synthesis tool automatically generates the respective gates. module p1(x,y,z); input x,y; output z; wor p; assign p=x&y; assign p=~x&~y; assign z=p; endmodule module p2(x,y,z); input x,y; output z; wire p; assign p=x&y; assign p=~x&~y; assign z=p; endmodule module p3(x,y,z); input x,y: output z; wire p,q ; assign p=x&y; assign q=~x&~y; assign z=p|q; endmodule WRONG CODE GENERAL CODE

- 52. 21/01/2019 52Aravinda K., Dept. of E&C, NHCE Verilog operators Unary Arithmetic + plus - minus ! logical negation ~ bitwise negation & reduction AND | reduction OR ^ reduction XOR Relational and shift + add - subtract * multiply / divide % modulus ** exponent < less than > greater than <= less than or equal >= greater than or equal << logical left shift >> logical right shift <<< arithmetic left shift >>> arithmetic right shift

- 53. 21/01/2019 53Aravinda K., Dept. of E&C, NHCE Verilog operators contd… Logical Bitwise == equality != inequality === case equality !== case inequality && logical AND || logical OR Other & AND | OR ^ XOR ^~ ~^ equal ?: conditional {} concatenation {{}} replication

- 54. 21/01/2019 54Aravinda K., Dept. of E&C, NHCE

- 55. 21/01/2019 55Aravinda K., Dept. of E&C, NHCE Expression Operation Result C >> 2 Shift right by 2 places 000110 C >> 2 & D Bitwise AND 000010 ~ B Bitwise INVERT 000 {A, ~B} Concatenate 110000 ({A, ~B}) | (C >> 2 & D) Bitwise OR 110010 (({A, ~B}) | (C >> 2 & D)) & D Bitwise AND 110010 (({A, ~B}) | (C >> 2 & D)) & D == 110010 Equality check TRUE Example: A = 110, B = 111, C = 011000, D = 111011

- 56. 21/01/2019 56Aravinda K., Dept. of E&C, NHCE Unary reduction reduces a vector into a single bit. When parentheses are not used, “Unary” operators have the highest precedence and “Other” operators have the lowest precedence, in the class in which the operators are listed. Operators belonging to the same class have same precedence, and are applied from left to right in an expression. & && Operates on Boolean type as well as on binary data Operates only on the Boolean data type (TRUE or FALSE) Evaluates both sides of the expression Evaluates only the LHS of the expression When A = 5, B = 4, C = 3, then (A>=B) && (B<=C) yields (1) && (0) yields (0).

- 57. 21/01/2019 57Aravinda K., Dept. of E&C, NHCE Expression Operation Result A >> 4 Logical right shift 00001010 A >>> 4 Arithmetic right shift 11111010 A << 4 Logical left shift 01010000 A <<< 4 Arithmetic left shift 01010000 reg signed [7:0] A = 8’hA5; (A = 10100101) Expression Operation Result B >> 4 Logical right shift 00001010 B >>> 4 Arithmetic right shift 00001010 B << 4 Logical left shift 01010000 B <<< 4 Arithmetic left shift 01010000 reg [7:0] B = 8’hA5; (B = 10100101)

- 58. 21/01/2019 58Aravinda K., Dept. of E&C, NHCE Expression Operation Result A >> 4 Logical right shift 00001010 A >>> 4 Arithmetic right shift 00001010 A << 4 Logical left shift 01010000 A <<< 4 Arithmetic left shift 01010000 integer signed A = 8’hA5; (A = 00000000000000000000000010100101) integer A = 8’shA5; (A = 11111111111111111111111110100101) Expression Operation Result A >> 4 Logical right shift 11111010 A >>> 4 Arithmetic right shift 11111010 A << 4 Logical left shift 01010000 A <<< 4 Arithmetic left shift 01010000

- 59. 21/01/2019 59Aravinda K., Dept. of E&C, NHCE Verilog models for Multiplexers The expression for the output is, F = A’I0+AI1

- 60. 21/01/2019 60Aravinda K., Dept. of E&C, NHCE The expression for the output is, F = A’B’I0+A’BI1+AB’I2+ABI3 Code with the procedural assignment, using the “case” statement Code with the continuous statement

- 61. 21/01/2019 61Aravinda K., Dept. of E&C, NHCE Code with the procedural assignment, using the “if” statement Important coding practices while writing synthesizable Verilog: 1. Whenever possible, use concurrent assignments to design the combinational logic. 2. Whenever procedural assignments are used for the combinational logic, use blocking assignments. 3. Use “always @(*)”, to avoid accidental omissions of inputs in the sensitivity list.

- 62. 21/01/2019 62Aravinda K., Dept. of E&C, NHCE Modeling Registers and Counters Cyclic shift register

- 63. 21/01/2019 63Aravinda K., Dept. of E&C, NHCE Concurrent Blocking Non-blocking assign y = a & b; y = a & b; y <= a & b; Assignment is immediate Assignment is immediate Assignment is parallel Suitable for combinational logic Suitable for combinational logic Suitable for sequential logic Order of the statements is not important Order of the statements is important Order of the statements is not important

- 64. 21/01/2019 64Aravinda K., Dept. of E&C, NHCE Synthesis output: A 3-bit shift register, with serial input A, and outputs Q1, Q2, Q3. Synthesis output: A single flip- flop, with input A, and a single output Q3.

- 65. 21/01/2019 65Aravinda K., Dept. of E&C, NHCE 1. Register with synchronous “clear” and “load” 2. Register with “left shift” operation and concatenation

- 66. 21/01/2019 66Aravinda K., Dept. of E&C, NHCE 3. Synchronous counter 4. Standard synchronous counter, 74163

- 67. 21/01/2019 67Aravinda K., Dept. of E&C, NHCE P is “enable” signal and T is “carry connection” signal. “clear” overrides “load” and “count” functions, and “load” overrides “count” function.

- 68. 21/01/2019 68Aravinda K., Dept. of E&C, NHCE This is a structural modeling, which interconnects the previous defined modules. c74163 is component’s name; ct1, ct2 are instance names. 5. Cascading of 74163, to get 8-bit counter

- 69. 21/01/2019 69Aravinda K., Dept. of E&C, NHCE Synthesis of “Left shift” register Verilog cannot synthesize delays. Similarly, “initial” blocks are ignored by the synthesis tools.

- 70. 21/01/2019 70Aravinda K., Dept. of E&C, NHCE This code is meant for a combinational circuit, but creates an additional latch to hold the value of F, when Sel changes to 2’b11. This latch creates timing issues. The additional latch can be avoided, if all possible cases of the inputs are included. When all possible execution paths are covered, holding a value is not necessary. The additional latch can also be avoided, by initializing the combinational output in the beginning of “always” block. In this way, holding a value becomes unnecessary.

- 71. 21/01/2019 71Aravinda K., Dept. of E&C, NHCE Important coding practices while writing synthesizable Verilog: 4. Use an edge-triggered clock in the sensitivity list (using the “posedge” or “negedge” keywords). 5. Should not make assignments to the same variable, in more than one “always” block. 6. Unwanted latches can be avoided, by means of – i) including “else” clauses for “if” statements. ii) specifying all cases for “case” statements, or having a “default” clause at the end. iii) initializing the combinational outputs at the beginning of the “always” block.

- 72. 21/01/2019 72Aravinda K., Dept. of E&C, NHCE Behavioral and Structural Verilog Any circuit can be represented in multiple forms of abstraction; e.g., different designers think of NAND gate in different representations. In the same way, the function F = AB + BC can be described in two different ways:

- 73. 21/01/2019 73Aravinda K., Dept. of E&C, NHCE Behavioral models Data flow (RTL) models Structural models These models describe the system at a higher level of abstraction, without implying any particular structure or technology. (e.g., full adder’s truth table description) These models describe the system at a lower level of abstraction, by means of components and their interconnections. (e.g., full adder in terms of half adders) These models describe the system at an intermediate level, called as Register Transfer Language. (e.g.: full adder’s algebraic expressions)

- 74. EXAMPLE: SEQUENCE DETECTOR THAT DETECTS “101” Modeling a sequential machine 21/01/2019 Aravinda K., Dept. of E&C, NHCE 74

- 75. 21/01/2019 75Aravinda K., Dept. of E&C, NHCE Two types of finite state machines

- 76. 21/01/2019 76Aravinda K., Dept. of E&C, NHCE

- 77. 21/01/2019 77Aravinda K., Dept. of E&C, NHCE Behavioral modeling for a Mealy sequential circuit State table An example is the state machine of a BCD to excess-3 code converter, which can be designed in four different ways: 1. Behavioral: with two “always” blocks 2. Behavioral: with one “always” block 3. Data flow: with combinational logic 4. Structural: with combinational logic

- 78. 21/01/2019 78Aravinda K., Dept. of E&C, NHCE 1. With two “always” blocks: i) One for combinational part ii) Other for state register

- 79. 21/01/2019 79Aravinda K., Dept. of E&C, NHCE 2. With one “always” block When compared to this model, the earlier one is better because, it corresponds more closely to the hardware implementation.

- 80. 21/01/2019 80Aravinda K., Dept. of E&C, NHCE 3. With combinational logic (data flow model) This model requires state assignments, and the derivation of the next state equations.

- 81. 21/01/2019 81Aravinda K., Dept. of E&C, NHCE 4. With combinational logic (structural model) This model exactly corresponds to the hardware that was intended, but requires more effort to produce. Hence, to have quicker “time-to-market”, designers often use behavioral model.

- 82. 21/01/2019 82Aravinda K., Dept. of E&C, NHCE OF MODULE - 1

- 83. 21/01/2019 Aravinda K., Dept. of E&C, NHCE 83

![21/01/2019 27Aravinda K., Dept. of E&C, NHCE

When the signal is of type wire (or net), it generally has

a value of 0 or 1.

The net values in Verilog are represented as -

<number of bits>’<base><value>.

Hence, 1’b0 means “1 position binary 0”. The decimal and

hexadecimal values are represented with “d” and “h”.

A one-dimensional array of bit signals is referred to as a vector.

A 4 bit-wire can be named as vector B, and can be declared as,

wire B[3:0];.

The vector B has an index range 0 through 3, and its elements

are designated as B[0], B[1], B[2] and B[3].

The statement B=4’b1100 assigns 1 to B[3], 1 to B[2], 0 to B[1]

and 0 to B[0].](https://image.slidesharecdn.com/sdhdlece43-m1-200302071630/85/System-design-using-HDL-Module-1-27-320.jpg)

![21/01/2019 57Aravinda K., Dept. of E&C, NHCE

Expression Operation Result

A >> 4 Logical right shift 00001010

A >>> 4 Arithmetic right shift 11111010

A << 4 Logical left shift 01010000

A <<< 4 Arithmetic left shift 01010000

reg signed [7:0] A = 8’hA5;

(A = 10100101)

Expression Operation Result

B >> 4 Logical right shift 00001010

B >>> 4 Arithmetic right shift 00001010

B << 4 Logical left shift 01010000

B <<< 4 Arithmetic left shift 01010000

reg [7:0] B = 8’hA5;

(B = 10100101)](https://image.slidesharecdn.com/sdhdlece43-m1-200302071630/85/System-design-using-HDL-Module-1-57-320.jpg)

![VHDL_Lecture_new1 [Autosaved].ppt](https://cdn.slidesharecdn.com/ss_thumbnails/vhdllecturenew1autosaved-221108174421-ff4566f0-thumbnail.jpg?width=560&fit=bounds)