SystemVerilog Assertions verification with SVAUnit - DVCon US 2016 Tutorial

- 1. Tutorial SystemVerilog Assertions Verification with SVAUnit Andra Radu Ionu Ciocîrlanț

- 2. SVAUnit tutorial topics • Introduction to SystemVerilog Assertions (SVAs) • Planning SVA development • Implementation • SVA verification using SVAUnit • SVA test patterns 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 2

- 3. Introduction to SystemVerilog Assertions (SVAs) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 3

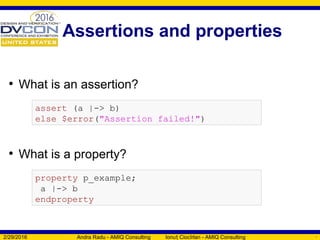

- 4. Assertions and properties • What is an assertion? • What is a property? 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 4 assert (a |-> b) else $error("Assertion failed!") property p_example; a |-> b endproperty

- 5. Simple assertion example 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 5 property req_to_rise_p; @(posedge clk) $rose(req) |-> ##[1:3] $rose(ack); endproperty ASSERT_LABEL: assert property (req_to_rise_p) else `uvm_error(“ERR", "Assertion failed")

- 6. Types of SystemVerilog Assertions • Immediate • Concurrent 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 6 assert (expression) pass_statement [else fail_statement]

- 7. Assertions are used • In a verification component • In a formal proof kit • In RTL generation “Revisiting Regular Expressions in SyntHorus2: from PSL SEREs to Hardware” (Fatemeh (Negin) Javaheri, Katell Morin-Allory, Dominique Borrione) • For test patterns generation “Towards a Toolchain for Assertion-Driven Test Sequence Generation” (Laurence PIERRE) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 7

- 8. SVAs advantages •Fast •Non-instrusive •Flexible •Coverable 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 8

- 9. Planning SVA development 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 9

- 10. Identify design characteristics • Defined in a document (design specification) • Known or specified by the designer • The most common format is of the form cause and effect: antecedent |-> consequent • Antecedent: • Consequent: 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 10 $rose(req) ##[1:3] $rose(ack)

- 11. Keep it simple. Partition! • Complex assertions are typically constructed from complex sequences and properties. 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 11 a ##1 b[*1:2] |=> c ##1 d[*1:2] |=> $fell(a) sequence seq(arg1, arg2); arg1 ##1 arg2[*1:2]; endsequence seq(a, b) |=> seq(c, d) |=> $fell(a)

- 12. Implementation 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 12

- 13. Coding guidelines • Avoid duplicating design logic in assertions • Avoid infinite assertions • Reset considerations • Mind the sampling clock 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 13

- 14. Coding guidelines (contd.) • Always check for unknown condition (‘X’) • Assertion naming • Detailed assertion messages • Assertion encapsulation 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 14

- 15. Best practices • Review the SVA with the designer to avoid DS misinterpretation • Use strong in assertions that may never complete: • Properties should not hold under certain conditions (reset, enable switch) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 15 assert property ( req |-> strong(##[1:$] ack)); assert property ( @(posedge clk) disable iff (!setup || !rst_n) req |-> strong(##[1:$] ack) );

- 16. Best practices (contd.) • Avoid overlapping assertions that contradict each other CPU_0: CPU_1: 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 16 assert property (WRITE |=> ERROR); assert property (WRITE |=> !ERROR); assert property (WRITE and CPU==0 |=> ERROR); assert property (WRITE and CPU==1 |=> !ERROR);

- 17. Best practices (contd.) • Use the $sampled() function in action blocks 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 17 Active Inactive NBA Observed Re-active Re-inactive Postponed Preponed Previous timeslot Next timeslot assert property ( @(posedge clk) ack == 0 ) else `uvm_error("ERROR", $sformatf("Assertion failed. ack is %d", $sampled(ack)));

- 18. Assertion example • AMBA APB protocol specification: The bus only remains in the SETUP state for one clock cycle and always moves to the ACCESS state on the next rising edge of the clock. 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 18

- 19. Assertion example (contd.) • Antecedent (the SETUP phase) • Consequent (the ACCESS phase) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 19 sequence setup_phase_s; $rose(psel) and $rose(pwrite) and (!penable) and (!pready); endsequence sequence access_phase_s; $rose(penable) and $rose(pready) and $stable(pwrite) and $stable(pwdata)and $stable(paddr) and $stable(psel); endsequence

- 20. Assertion example (contd.) • The property can be expressed as: • The assertion will look like: 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 20 property access_to_setup_p; @(posedge clk) disable iff (reset) setup_phase_s |=> access_phase_s; endproperty assert property (access_to_setup_p) else `uvm_error("ERR", "Assertion failed")

- 21. Does it work as intended? 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 21

- 22. SVA Verification with SVAUnit 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 22

- 23. SVA Verification Challenges 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 23 Clear separation between validation and SVA definition code Easy to: -Update -Enhance -Disable Results should be: - Deterministic -Repeatable Self-contained Adaptable Predictable

- 24. Introducing SVAUnit • Structured framework for Unit Testing for SVAs • Allows the user to decouple the SVA definition from its validation code • UVM compliant package written in SystemVerilog • Encapsulate each SVA testing scenario inside an unit test • Easily controlled and supervised using a simple API 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 24

- 25. SVAUnit Infrastructure 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 25 SVAUnit Testbench SVAUnit Test Suite SVAUnit Unit Test SVAUnit Test test() SVA interface handle Interface containing SVA Interface containing SVA SVAUnit Test SVAUnit Test Suite Reports Reports Reports Reports • SVAUnit Testbench - Enables SVAUnit - Instantiates SVA interface - Starts test • SVAUnit Test - Contains the SVA scenario • SVAUnit Test Suite - Test and test suite container

- 26. Example specification • AMBA APB protocol specification: The bus only remains in the SETUP state for one clock cycle and always moves to the ACCESS state on the next rising edge of the clock. 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 26

- 27. Example APB interface 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 27 interface apb_if (input pclk); logic psel; logic pwrite; logic penable; logic pready; logic [`ADDR_WIDTH-1 :0] paddr; logic [`WDATA_WIDTH-1:0] pwdata; endinterface APB sequences definitions APB property definition APB assertion definition

- 28. APB sequences definitions • Antecedent (the SETUP phase) • Consequent (the ACCESS phase) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 28 sequence setup_phase_s; $rose(psel) and $rose(pwrite) and (!penable) and (!pready); endsequence sequence access_phase_s; $rose(penable) and $rose(pready) and $stable(pwrite) and $stable(pwdata)and $stable(paddr) and $stable(psel); endsequence

- 29. APB property & assertion definitions • The property can be expressed as: • The assertion will look like: 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 29 property access_to_setup_p; @(posedge clk) disable iff (reset) setup_phase_s |=> access_phase_s; endproperty assert property (access_to_setup_p) else `uvm_error("ERR", "Assertion failed")

- 30. Example of SVAUnit Testbench 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 30 module top; // Instantiate the SVAUnit framework `SVAUNIT_UTILS ... // APB interface with the SVA we want to test apb_if an_apb_if(.clk(clock)); initial begin // Register interface with the uvm_config_db uvm_config_db#(virtual an_if):: set(uvm_root::get(), "*", “VIF", an_apb_if); // Start the scenarios run_test(); end ... endmodule

- 31. Example of SVAUnit Test 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 31 class ut1 extends svaunit_test; // The virtual interface used to drive the signals virtual apb_if apb_vif; function void build_phase(input uvm_phase phase); // Retrieve the interface handle from the uvm_config_db if (!uvm_config_db#(virtual an_if)::get(this, "", “VIF", apb_vif)) `uvm_fatal(“UT1_NO_VIF_ERR", "SVA interface is not set!") // Test will run by default; disable_test(); endfunction task test(); // Initialize signals // Create scenarios for SVA verification endtask endclass

- 32. APB – SVAUnit test steps 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 32 Enable the APB SVA Initialize the interface signals Generate setup phase stimuli Generate access phase stimuli SVA checks based on generated stimuli

- 33. Enable SVA and initialize signals 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 33 ... // Enable the APB SVA vpiw.disable_all_assertions(); vpiw.enable_assertion("APB_PHASES"); // Initialize signals task initialize_signals(); apb_vif.paddr <= 32'b0; apb_vif.pwdata <= 32'b0; apb_vif.pwrite <= 1'b0; apb_vif.penable <= 1'b0; apb_vif.psel <= 1'b0; endtask ...

- 34. Generate setup phase stimuli 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 34 ... task generate_setup_phase_stimuli(bit valid); ... // Stimuli for valid SVA scenario valid == 1 -> pwrite == 1 && psel == 1 && penable == 0 && pready == 0; // Stimuli for invalid SVA scenario valid == 0 -> pwrite != 1 || psel != 1 || penable != 0 || pready != 0; ... endtask ...

- 35. Generate access phase stimuli 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 35 ... task generate_access_phase_stimuli(bit valid); ... // Constrained stimuli for valid SVA scenario valid == 1 -> pwdata == apb_vif.pwdata && paddr == apb_vif.paddr && pwrite == 1 && psel == 1 && penable == 1 && pready == 1; // Constrained stimuli for invalid SVA scenario valid == 0 -> pwdata != apb_vif.pwdata || paddr != apb_vif.paddr || pwrite != 1 || psel != 1 || penable != 1 || pready != 1; ... endtask ...

- 36. SVA state checking 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 36 ... if (valid_setup_phase) if (valid_access_phase) vpiw.fail_if_sva_not_succeeded("APB_PHASES", "The assertion should have succeeded!"); else vpiw.fail_if_sva_succeeded("APB_PHASES", "The assertion should have failed!"); else vpiw.pass_if_sva_not_started("APB_PHASES", "The assertion should not have started!"); ...

- 37. Example of SVAUnit Test Suite 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 37 class uts extends svaunit_test_suite; // Instantiate the SVAUnit tests ut1 ut1; ... ut10 ut10; function void build_phase(input uvm_phase phase); // Create the tests using UVM factory ut1 = ut1::type_id::create("ut1", this); ... ut10 = ut10::type_id::create("ut10", this); // Register tests in suite `add_test(ut1); ... `add_test(ut10); endfunction endclass

- 38. SVAUnit Test API 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 38

- 39. SVAUnit Flow 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 39 Instantiate test in Test Suite Create an SVAUnit Test Suite Register tests in test suite Scan report Simulate Create SVAUnit Testbench Create an SVAUnit Test Implement test() task

- 40. Error reporting 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 40 Name of SVAUnit check Custom error message Name of SVA under test SVAUnit test path

- 41. Hierarchy report 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 41

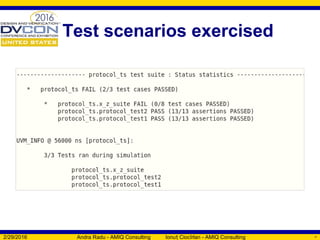

- 42. Test scenarios exercised 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 42

- 43. SVAs and checks exercised 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 43

- 44. SVA test patterns 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 44

- 45. Simple implication test 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 45 • a and b |=> c repeat (test_loop_count) begin randomize(stimuli_for_a, stimuli_for_b, stimuli_for_c); interface.a <= stimuli_for_a; interface.b <= stimuli_for_b; @(posedge an_vif.clk); interface.c <= stimuli_for_c; @(posedge interface.clk); @(posedge interface.clk); if (stimuli_for_a == 1 && stimuli_for_b == 1) if (stimuli_for_c == 1) vpiw.fail_if_sva_not_succeeded("IMPLICATION_ASSERT", "The assertion should have succeeded!"); else vpiw.fail_if_sva_succeeded("IMPLICATION_ASSERT", "The assertion should have failed!"); else vpiw.pass_if_sva_not_started("IMPLICATION_ASSERT", "The assertion should not have started!"); end

- 46. Multi-thread antecedent/consequent 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 46 • $rose(a) ##[1:4] b |-> ##[1:3] c repeat (test_loop_count) begin // Generate valid delays for asserting b and c signals randomize(delay_for_b inside {[1:4]}, delay_for_c inside {[1:3]}); interface.a <= 1; repeat (delay_for_b) @(posedge interface.clk); interface.b <= 1; vpiw.pass_if_sva_started_but_not_finished("MULTITHREAD_ASSERT", "The assertion should have started but not finished!"); repeat (delay_for_c) @(posedge interface.clk); interface.c <= 1; vpiw.pass_if_sva_succeeded("MULTITHREAD_ASSERT", "The assertion should have succeeded!"); end

- 47. Multi-thread antecedent/consequent (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 47 • $rose(a) ##[1:4] b |-> ##[1:3] c repeat (test_loop_count) begin // Generate invalid delays for asserting b and c signals randomize(delay_for_b inside {[0:10]}, delay_for_c inside {0,[4:10]}); interface.a <= 1; repeat (delay_for_b) @(posedge interface.clk); interface.b <= 1; vpiw.pass_if_sva_not_succeeded("MULTITHREAD_ASSERT", "The assertion should have failed!"); repeat (delay_for_c) @(posedge interface.clk); interface.c <= 1; if (delay_for_b < 5) vpiw.fail_if_sva_succeeded("MULTITHREAD_ASSERT", "The assertion should have failed!"); end

- 48. Consecutive repetition 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 48 • a |-> b[*1:2] ##1 c repeat (test_loop_count) begin randomize(stimuli_for_a, stimuli_for_c, number_of_b_cycles <= 2); interface.a <= stimuli_for_a; repeat (number_of_b_cycles) begin randomize(stimuli_for_b) interface.b <= stimuli_for_b; if (stimuli_for_b == 1) number_of_b_assertions += 1; @(posedge interface.clk); end if (stimuli_for_a == 1 && number_of_b_assertions == number_of_b_cycles && number_of_b_assertions > 0) vpiw.pass_if_sva_started_but_not_finished("IMPLICATION_ASSERT", "The assertion should have started but not finished!"); @(posedge interface.clk); ... // (continued on the next slide)

- 49. Consecutive repetition (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 49 • a |-> b[*1:2] ##1 c ... // (continued from previous slide) interface.c <= stimuli_for_c; @(posedge interface.clk); if (stimuli_for_a == 1) if (number_of_b_assertions != number_of_b_cycles || number_of_b_assertions == 0 || stimuli_for_c == 0) vpiw.fail_if_sva_succeeded("IMPLICATION_ASSERT", "The assertion should have failed!"); else vpiw.fail_if_sva_not_succeeded("IMPLICATION_ASSERT", "The assertion should have succeeded!"); end // end of test repeat loop

- 50. Repetition range with zero 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 50 • a |-> b[*0:2] ##1 c

- 51. Repetition range with zero (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 51 • a |-> b[*0:2] ##1 c

- 52. Sequence disjunction 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 52 • a |=> (b ##1 c) or (d ##1 e) repeat (test_loop_count) begin randomize(stimuli_for_a, stimuli_for_b, stimuli_for_c, stimuli_for_d, stimuli_for_e); interface.a <= stimuli_for_a; @(posedge interface.clk); fork begin end begin end join end Stimuli for branch: (b ##1 c) SVA state check based on branch stimuli Stimuli for branch: (c ##1 d) SVA state check based on branch stimuli

- 53. Sequence disjunction (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 53 • a |=> (b ##1 c) or (d ##1 e) ... // Stimuli for branch (b ##1 c) fork begin interface.b <= stimuli_for_b; @(posedge interface.clk); interface.c <= stimuli_for_c; @(posedge interface.clk); @(posedge interface.clk); // SVA state check based on branch stimuli sva_check_phase(interface.a, interface.b, interface.c); end join

- 54. Sequence disjunction (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 54 • a |=> (b ##1 c) or (d ##1 e) ... // Stimuli for branch (d ##1 e) fork begin interface.b <= stimuli_for_d; @(posedge interface.clk); interface.c <= stimuli_for_e; @(posedge interface.clk); @(posedge interface.clk); // SVA state check based on branch stimuli sva_check_phase(interface.a, interface.d, interface.e); end join

- 55. Sequence disjunction (contd.) 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 55 • a |=> (b ##1 c) or (d ##1 e) // SVA state checking task used in each fork branch task sva_check_phase(bit stimuli_a, bit stimuli_b, bit stimuli_c); if (stimuli_a) if (stimuli_b && stimuli_c) vpiw.pass_if_sva_succeeded("DISJUNCTION_ASSERT", "The assertion should have succeeded"); else vpiw.fail_if_sva_succeeded("DISJUNCTION_ASSERT", "The assertion should have failed"); endtask

- 56. Tools integration 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 56 Simulator independent!

- 57. Availability 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 57 • SVAUnit is an open-source package released by AMIQ Consulting • We provide: - SystemVerilog and simulator integration codes - AMBA-APB assertion package - Code templates and examples - HTML documentation for API https://github.com/amiq-consulting/svaunit

- 58. Conclusions • SVAUnit decouples the checking logic from SVA definition code • Safety net for eventual code refactoring • Can also be used as self-checking documentation on how SVAs work • Quick learning curve • Easy-to-use and flexible API • Speed up verification closure • Boost verification quality 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 58

- 59. Q & A ? 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 59

- 60. Thank you! 2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 60

![Simple assertion example

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 5

property req_to_rise_p;

@(posedge clk)

$rose(req) |-> ##[1:3] $rose(ack);

endproperty

ASSERT_LABEL: assert property (req_to_rise_p)

else `uvm_error(“ERR", "Assertion failed")](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-5-320.jpg)

![Types of SystemVerilog

Assertions

• Immediate

• Concurrent

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 6

assert (expression) pass_statement

[else fail_statement]](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-6-320.jpg)

![Identify design characteristics

• Defined in a document (design specification)

• Known or specified by the designer

• The most common format is of the form cause and

effect: antecedent |-> consequent

• Antecedent:

• Consequent:

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 10

$rose(req)

##[1:3] $rose(ack)](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-10-320.jpg)

![Keep it simple. Partition!

• Complex assertions are typically constructed from

complex sequences and properties.

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 11

a ##1 b[*1:2] |=> c ##1 d[*1:2] |=> $fell(a)

sequence seq(arg1, arg2);

arg1 ##1 arg2[*1:2];

endsequence

seq(a, b) |=> seq(c, d) |=> $fell(a)](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-11-320.jpg)

![Best practices

• Review the SVA with the designer to avoid DS

misinterpretation

• Use strong in assertions that may never complete:

• Properties should not hold under certain conditions

(reset, enable switch)

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 15

assert property ( req |-> strong(##[1:$] ack));

assert property (

@(posedge clk) disable iff (!setup || !rst_n)

req |-> strong(##[1:$] ack)

);](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-15-320.jpg)

![Example APB interface

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 27

interface apb_if (input pclk);

logic psel;

logic pwrite;

logic penable;

logic pready;

logic [`ADDR_WIDTH-1 :0] paddr;

logic [`WDATA_WIDTH-1:0] pwdata;

endinterface

APB sequences definitions

APB property definition

APB assertion definition](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-27-320.jpg)

![Multi-thread

antecedent/consequent

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 46

• $rose(a) ##[1:4] b |-> ##[1:3] c

repeat (test_loop_count) begin

// Generate valid delays for asserting b and c signals

randomize(delay_for_b inside {[1:4]}, delay_for_c inside {[1:3]});

interface.a <= 1;

repeat (delay_for_b)

@(posedge interface.clk);

interface.b <= 1;

vpiw.pass_if_sva_started_but_not_finished("MULTITHREAD_ASSERT",

"The assertion should have started but not finished!");

repeat (delay_for_c)

@(posedge interface.clk);

interface.c <= 1;

vpiw.pass_if_sva_succeeded("MULTITHREAD_ASSERT",

"The assertion should have succeeded!");

end](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-46-320.jpg)

![Multi-thread

antecedent/consequent (contd.)

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 47

• $rose(a) ##[1:4] b |-> ##[1:3] c

repeat (test_loop_count) begin

// Generate invalid delays for asserting b and c signals

randomize(delay_for_b inside {[0:10]}, delay_for_c inside {0,[4:10]});

interface.a <= 1;

repeat (delay_for_b)

@(posedge interface.clk);

interface.b <= 1;

vpiw.pass_if_sva_not_succeeded("MULTITHREAD_ASSERT",

"The assertion should have failed!");

repeat (delay_for_c)

@(posedge interface.clk);

interface.c <= 1;

if (delay_for_b < 5)

vpiw.fail_if_sva_succeeded("MULTITHREAD_ASSERT",

"The assertion should have failed!");

end](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-47-320.jpg)

![Consecutive repetition

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 48

• a |-> b[*1:2] ##1 c

repeat (test_loop_count) begin

randomize(stimuli_for_a, stimuli_for_c, number_of_b_cycles <= 2);

interface.a <= stimuli_for_a;

repeat (number_of_b_cycles) begin

randomize(stimuli_for_b)

interface.b <= stimuli_for_b;

if (stimuli_for_b == 1) number_of_b_assertions += 1;

@(posedge interface.clk);

end

if (stimuli_for_a == 1 && number_of_b_assertions == number_of_b_cycles &&

number_of_b_assertions > 0)

vpiw.pass_if_sva_started_but_not_finished("IMPLICATION_ASSERT",

"The assertion should have started but not finished!");

@(posedge interface.clk);

... // (continued on the next slide)](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-48-320.jpg)

![Consecutive repetition

(contd.)

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 49

• a |-> b[*1:2] ##1 c

...

// (continued from previous slide)

interface.c <= stimuli_for_c;

@(posedge interface.clk);

if (stimuli_for_a == 1)

if (number_of_b_assertions != number_of_b_cycles ||

number_of_b_assertions == 0 ||

stimuli_for_c == 0)

vpiw.fail_if_sva_succeeded("IMPLICATION_ASSERT",

"The assertion should have failed!");

else

vpiw.fail_if_sva_not_succeeded("IMPLICATION_ASSERT",

"The assertion should have succeeded!");

end // end of test repeat loop](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-49-320.jpg)

![Repetition range with zero

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 50

• a |-> b[*0:2] ##1 c](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-50-320.jpg)

![Repetition range with zero

(contd.)

2/29/2016 Andra Radu - AMIQ Consulting Ionu Ciocîrlan - AMIQ Consultingț 51

• a |-> b[*0:2] ##1 c](https://image.slidesharecdn.com/systemverilogassertionsverificationwithsvaunit-160809143424/85/SystemVerilog-Assertions-verification-with-SVAUnit-DVCon-US-2016-Tutorial-51-320.jpg)