Upgrading to SystemVerilog for FPGA Designs - FPGA Camp Bangalore, 2010

- 1. Upgrading to SystemVerilog for FPGA Designs - Presented at FPGA Camp, Bangalore Srinivasan Venkataramanan Chief Technology Officer CVC Pvt. Ltd. www.cvcblr.com

- 2. Agenda Introduction to SystemVerilog (SV) SV - RTL Design constructs SV Interface SV Assertions Success Stories SV-FPGA Ecosystem CVC Copyright 2008 2 www.cvcblr.com

- 3. About the presenter Srinivasan Venkataramanan, CTO, www.cvcblr.com http://www.linkedin.com/in/svenka3 Over 13 years of experience in VLSI Design & Verification Designed, verified and lead several multi-million ASICs in image processing, networking and communication domain Worked at Philips, Intel, Synopsys in various capacities. Co-authored leading books in the Verification domain. Presented papers, tutorials in various conferences, publications and avenues. Conducted workshops and trainings on PSL, SVA, SV, VMM, E, ABV, CDV and OOP for Verification Holds M.Tech in VLSI Design from prestigious IIT, Delhi. CVC Copyright Protected Material, www.cvcblr.com 3

- 4. What is SystemVerilog? Superset of Verilog-2001 IEEE 1800-2005 standard More information @ www.SystemVerilog.org Several books available: SystemVerilog Assertions Handbook – Ajeetha, Ben Cohen, Srinivasan, www.systemverilog.us A Pragmatic approach to VMM adoption – Ajeetha, Ben, Srinivasan SystemVerilog for Designers, Stuart Sutherland CVC Copyright 2008 4 www.cvcblr.com

- 5. SystemVerilog - Evolution Classes, Temporal Sequential inheritance, Property Regular Definitions Expressions OOP based polymorphism Testbench Properties – capture temporal Constraint driven Constrained randomization Behavior: Assertion, Functional Coverage Semaphores Random Data Assumption, Coverage Inheritance Mailboxes Generation SVA Polymorphism Queues, Covergroup, Virtual Interface MDAs Data structures Associative sampling enums & Dynamic arrays Strings Enhanced programming Verilog 2001 (do while, break, continue, ++, --, +=. Etc.) DPI – Quickly connect C/C++ Enhanced Design Coverage & Very efficient and ease of use Assertion API Better logical blocks – Constructs, modeling always_comb, _ff, _latch SV-Design DPI interface CVC Copyright 2008 5 www.cvcblr.com

- 6. SystemVerilog - User view Has 5 major parts: SVD – SystemVerilog for Design SVA – SystemVerilog Assertions SVTB – SystemVerilog Testbench SV-DPI – Direct Programming Interface for better C/C++ interface SV-API – Application Procedural Interface for Coverage, Assertion etc. CVC Copyright 2008 6 www.cvcblr.com

- 7. Reference Books Source A Pragmatic Approach to VMM Adoption 2006 for Tutorial ISBN 0-9705394-9-5, http://www.systemverilog.us and Code (7) CVC Copyright 2009

- 8. SV Design-Data Types Enhanced data types: 2-state (bit), logic Potential memory & run time improvement (2-state) High level models can avail 2-state Clearer descriptions: a Verilog reg is NOT necessarily a “register” CVC Copyright 2008 8 www.cvcblr.com

- 9. SV Design – Data types User Defined types Enums – local, typedef Strict type checking, typecast Better modeling style, easy to read, maintain State encoding - via language (not via tool scripts) Ease of debug, waveform CVC Copyright 2008 9 www.cvcblr.com

- 10. SV Design – logic modeling Verilog RTL – only always block Combinatorial & Sequential Inference by sensitivity list One of the top 10 error prone usages – more for newbie SV: Enhanced Modeling always_comb always_ff always_latch CVC Copyright 2008 10 www.cvcblr.com

- 11. What logic is being modeled? Modeling combinatorial logic? Use always_comb Modeling Sequential logic? Use always_ff CVC Copyright 2008 11 www.cvcblr.com

- 12. What logic is being modeled? Modeling Latch? Use always_latch Reduces Synthesis- Simulation discrepancies Language captures design intent (not pragmas, tool settings) CVC Copyright 2008 12 www.cvcblr.com

- 13. Abstract modeling - struct C-like struct Well proven data structure abstraction technique Cut down CVC Copyright 2008 # lines 13 www.cvcblr.com

- 14. CVC Copyright Protected Material, www.cvcblr.com 14

- 15. Interfaces – bread-n-butter of modern SoCs CVC Copyright 2008 15 www.cvcblr.com

- 16. Interfaces – SPI, OCP CVC Copyright 2009 www.cvcblr.com 16

- 17. Old fashioned hook-up– Verilog description Too verbose Highly error prone Maintenance head-ache Not easy to CVC Copyright 2009 www.cvcblr.com reuse 17

- 18. Typical sub-systemusing Verilog Modeled AHB AHB Master1 Master2 AHB AHB Slave1 Slave2 SoC is built using IPs – lot of ReUse Individual blocks pre-verified in standalone Most Bugs Occur Between Blocks A good number of “Wiring” Errors CVC Copyright Protected Material, www.cvcblr.com 18

- 19. Hookup various blocks – the old way addr module top(); top mem_controller mc (clk, rst_n, dout, addr, din, wr_rd); Mem_Controller din memory mem0(clk,rst_n, addr, din, wr_rd, dout); wr_rd Memory endmodule module mem_controller ( dout input clk, rst_n,[7:0] dout, output [3:0] addr, [7:0] din, wr_rd); module memory(output [7:0] dout, task write(); input clk, rst_n, [3:0] addr, addr <= ‘haa; [7:0] din, wr_rd); din <= $random; always @(posedge clk) wr_rd = 1’b1; if (wr_rd) @(posedge clk); mem[addr] <= din; wr_rd = 1’b0; endmodule : memory endtask : write CVC Copyright Protected endmodule Material, www.cvcblr.com 19

- 20. Interface interface simple_bus; // Define the interface module cpuMod(simple_bus b, input bit logic req, gnt; clk); ... logic [7:0] addr, data; endmodule logic [1:0] mode; logic start, rdy; endinterface: simple_bus module top; logic clk = 0; simple_bus sb_intf; // Instantiate the module memMod(simple_bus a, // Use the interface simple_bus interface memMod mem(sb_intf, clk); input bit clk); cpuMod cpu(.b(sb_intf), .clk(clk)); logic avail; endmodule // a.req is the req signal in the ’simple_bus’ interface always @(posedge clk) a.gnt <= a.req & avail; endmodule CVC Copyright 2008 20 www.cvcblr.com

- 21. Assertion-Based Verification It’s a verification technique Instruments requirements with assertions Clarifies requirements with executable language Enables tools to preview assertion waveforms Instruments design with assertions Added visibility White-box testing into its internal state Provision for functional coverage information CVC Copyright 2008 21 www.cvcblr.com

- 22. Applying ABV - Bus based SoC Simulate What happened during sim? Any protocol violation? How many RW? Was xfer interrupted? CVC Copyright 2008 22 www.cvcblr.com

- 23. Use assertions sparingly Non-intrusive Works with any existing flow The more you add, the more you gain CVC Copyright 2008 23 www.cvcblr.com

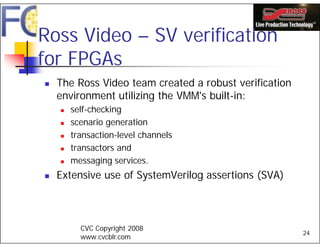

- 24. Ross Video – SV verification for FPGAs The Ross Video team created a robust verification environment utilizing the VMM's built-in: self-checking scenario generation transaction-level channels transactors and messaging services. Extensive use of SystemVerilog assertions (SVA) CVC Copyright 2008 24 www.cvcblr.com

- 25. Advantages of interface customer success stories Better design style Disambiguate the communication Forces to have a clear interface specification upfront – takes little more time, but saves much more later on Reduces integration time Add Assertions to interface, every block using it shall have to comply with the protocol CVC Copyright Protected Material, www.cvcblr.com 25

- 26. Impact of Interface module netproc (SX_ux_soc, SX_ux_en, SX_ux_data, SX_ux_clav, interface utopia_i; SX_ux_clk, SX_cpu_BusMode, SX_cpu_Addr, SX_cpu_Sel, wire soc; // start of cell SX_cpu_Data, SX_cpu_Rd_DS, SX_cpu_Wr_RW, wire en; // enable SX_cpu_Rdy_Dtack, rst, clk); inout SX_ux_soc; SystemVerilog wire [7:0] data; // data wire clav; // cell available inout SX_ux_en; wire clk; // ATM layer clock inout [7:0] SX_ux_data; endinterface inout SX_ux_clav; Verilog95 inout SX_ux_clk; interface cpu_i(input bit rst); inout SX_cpu_BusMode; wire BusMode; inout [11:0] SX_cpu_Addr; logic [11:0] Addr; inout SX_cpu_Sel; logic Sel; inout [7:0] SX_cpu_Data; wire [ 7:0] Data; inout SX_cpu_Rd_DS; logic Rd_DS; inout SX_cpu_Wr_RW; logic Wr_RW; inout SX_cpu_Rdy_Dtack; wire Rdy_Dtack; input rst; endinterface input clk; wire SX_ux_soc; module netproc(utopia_i ux, cpu_i cpu, wire SX_ux_en; input bit clk); wire [7:0] SX_ux_data; endmodule wire SX_ux_clav; wire SX_ux_clk; wire SX_cpu_BusMode; wire [11:0] SX_cpu_Addr; wire SX_cpu_Sel; wire [7:0] SX_cpu_Data; - 3X more compact wire SX_cpu_Rd_DS; wire SX_cpu_Wr_RW; - Fewer wiring mistakes wire SX_cpu_Rdy_Dtack; wire rst; wire clk; endmodule 26

- 27. Ecosystem around SV-FPGA All major EDA vendors support SV for Design (simulators) Synthesis: Synplify, leonardo FPGA vendors – need more support Latest update pending Books, tutorials – plenty: www.aldec.com/Downloads Trainings: www.cvcblr.com/trainings CVC Copyright Protected Material, www.cvcblr.com 27

- 28. Aldec’s Active-HDL Design-flow manager CVC Copyright Protected Material, www.cvcblr.com 28

- 29. SV & FPGA tool support Active-HDL SV-Design, Assertions (SVA + PSL) Interface, Debug Modelsim-DE SV-Design, SVA, PSL Synplify SV-Design, synthesizable constructs Leonardo Details awaited, call Mentor Xilinx, Altera Unknown, call your vendor CVC Copyright Protected Material, www.cvcblr.com 29

- 30. SV & FPGA advanced technologies With adoption of SV, modern design paradigms emerge ASIC prototyping – EVE Design systems Jasper’s ActiveDesign is one such technology Can create waveforms for AHB, AXI etc. right from RTL No TB required, plain RTL + ActiveDesign CVC Copyright Protected Material, www.cvcblr.com 30

- 31. Jasper’s ActiveDesign Capture “information” during RTL design phase: Designer makes an assumption about the latency of output, FIFO size etc. “show me a proof/witness/waveform” for such an occurrence Can we optimize the latency to say 5 What-if I change the FIFO size to 32 here etc. CVC Copyright Protected Material, www.cvcblr.com 31

- 32. CVC Trainings – www.cvcblr.com/trainings Verification Centric Course Comprehensive Functional Verification (CFV) Language Course IEEE 1800 SystemVerilog for Design (SVD) IEEE 1800 SystemVerilog Assertions (SVA) IEEE 1800 SystemVerilog for Verification (SVTB) IEEE 1850 Property Specification Language (PSL) IEEE 1647, E Methodology VMM, OVM, AVM, CDV, ABV Workshops Gate Level Simulation (GLS) ABV Beyond RTL (ABV) Coverage Driven Verification (CDV) OOP for functional Verification CVC Copyright 2009 www.cvcblr.com 32

- 33. CVC Publications, tutorials, workshops •Quick start guides, Tutorials • SVA • PSL • VMM •Workshops : •Gate Level Simulation •ABV beyond RTL •Coverage Driven Verification •OOP for Verification 33

- 34. CVC Copyright Protected Material, www.cvcblr.com 34

![Hookup various blocks – the old way

addr module top();

top mem_controller mc (clk, rst_n, dout,

addr, din, wr_rd);

Mem_Controller

din memory mem0(clk,rst_n, addr, din,

wr_rd, dout);

wr_rd Memory endmodule

module mem_controller (

dout input clk, rst_n,[7:0] dout,

output [3:0] addr, [7:0] din,

wr_rd);

module memory(output [7:0] dout, task write();

input clk, rst_n, [3:0] addr, addr <= ‘haa;

[7:0] din, wr_rd); din <= $random;

always @(posedge clk) wr_rd = 1’b1;

if (wr_rd) @(posedge clk);

mem[addr] <= din; wr_rd = 1’b0;

endmodule : memory endtask : write

CVC Copyright Protected endmodule

Material, www.cvcblr.com

19](https://image.slidesharecdn.com/vowsvforfpgascamp2010-100521054620-phpapp01/85/Upgrading-to-SystemVerilog-for-FPGA-Designs-FPGA-Camp-Bangalore-2010-19-320.jpg)

![Interface

interface simple_bus; // Define the interface module cpuMod(simple_bus b, input bit

logic req, gnt; clk);

...

logic [7:0] addr, data;

endmodule

logic [1:0] mode;

logic start, rdy;

endinterface: simple_bus module top;

logic clk = 0;

simple_bus sb_intf; // Instantiate the

module memMod(simple_bus a, // Use the interface

simple_bus interface memMod mem(sb_intf, clk);

input bit clk); cpuMod cpu(.b(sb_intf), .clk(clk));

logic avail; endmodule

// a.req is the req signal in the ’simple_bus’

interface

always @(posedge clk) a.gnt <= a.req &

avail;

endmodule CVC Copyright 2008

20

www.cvcblr.com](https://image.slidesharecdn.com/vowsvforfpgascamp2010-100521054620-phpapp01/85/Upgrading-to-SystemVerilog-for-FPGA-Designs-FPGA-Camp-Bangalore-2010-20-320.jpg)

![Impact of Interface

module netproc (SX_ux_soc, SX_ux_en, SX_ux_data, SX_ux_clav,

interface utopia_i; SX_ux_clk, SX_cpu_BusMode, SX_cpu_Addr, SX_cpu_Sel,

wire soc; // start of cell SX_cpu_Data, SX_cpu_Rd_DS, SX_cpu_Wr_RW,

wire en; // enable SX_cpu_Rdy_Dtack, rst, clk);

inout SX_ux_soc;

SystemVerilog

wire [7:0] data; // data

wire clav; // cell available inout SX_ux_en;

wire clk; // ATM layer clock inout [7:0] SX_ux_data;

endinterface inout SX_ux_clav;

Verilog95

inout SX_ux_clk;

interface cpu_i(input bit rst); inout SX_cpu_BusMode;

wire BusMode; inout [11:0] SX_cpu_Addr;

logic [11:0] Addr; inout SX_cpu_Sel;

logic Sel; inout [7:0] SX_cpu_Data;

wire [ 7:0] Data; inout SX_cpu_Rd_DS;

logic Rd_DS; inout SX_cpu_Wr_RW;

logic Wr_RW; inout SX_cpu_Rdy_Dtack;

wire Rdy_Dtack; input rst;

endinterface input clk;

wire SX_ux_soc;

module netproc(utopia_i ux, cpu_i cpu, wire SX_ux_en;

input bit clk); wire [7:0] SX_ux_data;

endmodule wire SX_ux_clav;

wire SX_ux_clk;

wire SX_cpu_BusMode;

wire [11:0] SX_cpu_Addr;

wire SX_cpu_Sel;

wire [7:0] SX_cpu_Data;

- 3X more compact wire SX_cpu_Rd_DS;

wire SX_cpu_Wr_RW;

- Fewer wiring mistakes wire SX_cpu_Rdy_Dtack;

wire rst;

wire clk;

endmodule 26](https://image.slidesharecdn.com/vowsvforfpgascamp2010-100521054620-phpapp01/85/Upgrading-to-SystemVerilog-for-FPGA-Designs-FPGA-Camp-Bangalore-2010-26-320.jpg)