Verilog hdl

- 1. Verilog HDL Gookyi Dennis A. N. ([email protected]) May.27.2014

- 2. Contents Module Modeling Styles Modules Structural Modeling Dataflow Modeling Behavioral Modeling Mixed-Style Modeling Simulation Basic Simulation Constructs Related Compiler Directive and System Tasks 2

- 3. Modules A Verilog HDL module consist of two major parts: The interface The internal (body) Block diagram of a full adder is shown below 3

- 4. The Interface: Port Declaration The interface signals can be grouped into one of the following three types: input, output or inout A complete interface can be divided into three parts: port list, port declaration and data type declaration 4

- 5. Port Declaration The declaration of a port and its associated data type can be combined into a single line as below: Port list, port declaration and their associated data types can be put into a single list. This is called port list declaration or ANSI C style 5

- 6. Port Connections Two methods are used to connect ports to external signals: Named association: ports to be connected to external signals are specified by listing their names. The order of the ports is not important Positional association: the signals to be connected must have the same order as in the port list. All unconnected ports are left blank The two methods cannot be mixed 6

- 8. Modeling the Internal of a Module The internal or body can be modeled using one of the following styles: Structural Style Gate level Switch level Dataflow Style Behavioral Style Mixed Style RTL = Behavioral + Dataflow Styles 8

- 9. Structural Modeling Structural modeling of a design is by connecting required instantiations of built-in primitives, user defined primitives or other modules through nets Structural style is one way to model a complex digital system in a hierarchical manner 9

- 11. Dataflow Modeling The module is described by specifying the data flow between registers and how the data is processed This is done through a set of continuous assignment statements A continuous assignment starts with the keyword assign and has a syntax as below: assign [delay] l_value = expression; 11

- 12. Dataflow Modeling The block diagram of a full adder is shown below: 12

- 13. Waveform 13

- 14. Behavioral Modeling The module is described in terms of the desired design algorithm without concerning the hardware implementation details The module uses procedural constructs: initial and always 14

- 15. Mixed modeling The design is described in terms of the mixing of the previous styles It is most commonly used in modeling large designs Register-Transfer level (RTL) is usually used in industry to mean the combination of behavioral and dataflow constructs Below is a full adder constructed with basic logic gates: 15

- 17. Simulation For a design to be useful, it must be verified to make sure that it can operate according to the requirement Two basic simulation structures are available in Verilog: The first is to take the UUT as an instantiated module in the stimulus module The second considers both stimulus block and UUT as the separate instantiated module at the top-level module 17

- 18. Related Compiler Directives: `timescale Directive In simulations, we need to specify the physical unit of measure This is accomplished using: `timescale time_unit/time_precision time unit : This is the time to be used as one unit for all the delays used in the design. time precision : This represents the minimum delay which needs to be considered during simulation or it decides that how many decimal point would be used with the time unit. 18

- 19. `timescale Directive Code Waveform 19

- 20. `timescale Directive Code Waveform 20

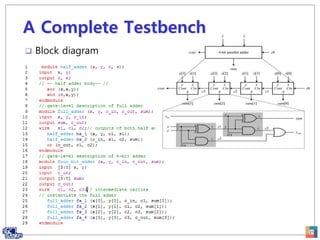

- 21. A Complete Testbench Block diagram 21

- 23. Waveform 23

![Dataflow Modeling

The module is described by specifying the data flow

between registers and how the data is processed

This is done through a set of continuous assignment

statements

A continuous assignment starts with the keyword assign

and has a syntax as below:

assign [delay] l_value = expression;

11](https://image.slidesharecdn.com/veriloghdl-140529090200-phpapp01/85/Verilog-hdl-11-320.jpg)